# JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

1/2005

Advanced silicon devices and technologies for ULSI era

Special issue edited by Andrzej Jakubowski and Lidia Łukasiak

Challenges in scaling of CMOS devices towards 65 nm node

#### Part 2

| Chancing of Civios devices towards of him node                                                                               |                 |     |

|------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

| M. Jurczak et al.                                                                                                            | Invited paper   | 3   |

| Gate dielectrics: process integration issues and electrical properties                                                       |                 |     |

| U. Schwalke                                                                                                                  | Invited paper   | 7   |

| Understanding of wet and alternative particle removal processe in microelectronics: theoretical capabilities and limitations | es              |     |

| F. Tardif, A. Danel, and O. Raccurt                                                                                          | (Invited paper) | -H  |

| Integrated gas chromatograph                                                                                                 |                 |     |

| J. A. Dziuban, J. Mróz, and J. Koszur                                                                                        | (Invited paper) | 20  |

| Low frequency noise in advanced Si bulk and SOI MOSFETs                                                                      |                 |     |

| J. Jomaah, F. Balestra, and G. Ghibaudo                                                                                      | Invited paper   | 24  |

| Variability of the local $\phi_{MS}$ values over the gate area of MOS devices                                                |                 |     |

| H. M. Przewłocki et al.                                                                                                      | Invited paper   | 34  |

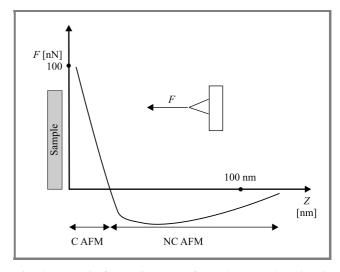

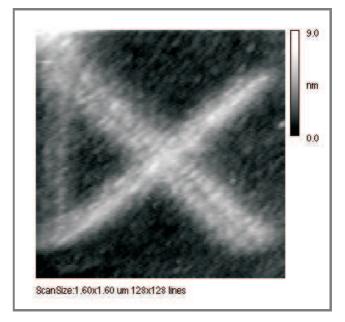

| Diagnostics of micro- and nanostructure using the scanning probe microscopy                                                  |                 |     |

| T. Gotszalk et al.                                                                                                           | Invited paper   | -41 |

| An accurate prediction of high-frequency circuit behaviour                                                                   |                 |     |

| S. Yoshitomi et al.                                                                                                          | Invited paper   | 47  |

| Trends in assembling of advanced IC packages                                                                                 |                 |     |

| R. Kisiel and Z. Szczepański                                                                                                 | (Invited paper) | 63  |

#### Editorial Board

Editor-in Chief: ...... Paweł Szczepański Krzysztof Borzycki Associate Editors: ..... Marek Jaworski Managing Editor: Maria Lopuszniak Technical Editor: Anna Tyszka-Zawadzka

### Editorial Advisory Board

Chairman: Andrzej Jajszczyk

Marek Amanowicz

Daniel Rem

Wojciech Burakowski

Andrzej Dąbrowski

Andrzej Hildebrandt

Witold Holubowicz

Andrzej Jakubowski

Alina Karwowska-Lamparska

Marian Kowalewski

Andrzej Kowalski

Józef Lubacz

Tadeusz Luba

Krzysztof Malinowski

Marian Marciniak

Józef Modelski

Ewa Orlowska

Andrzej Pach

Zdzisław Papir

Michal Pióro

Janusz Stokłosa

Włestaw Traczyk

Andrzej P. Wierzbicki

Tadeusz Więckowski

Józef Wożniak

Tadeusz A. Wysocki

Jan Zabrodzki

Andrzej Zieliński

ISSN 1509-4553 © Copyright by National Institute of Telecommunications Warsaw 2005

Circulation: 300 copies

Sowa - Druk na życzenie, www.sowadruk.pl, tel. 022 431-81-40

# JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

## **Preface**

Despite the fact that a range of limitations are beginning to appear as CMOS technology is being raised to ever higher levels of perfection, it is anticipated that silicon will be the dominant material of the semiconductor industry for at least the first half of the 21st century. The forecast for microelectronics development published in 2001 by SIA (Semiconductor Industry Association) reaches ahead to the years 2010–2016. Moreover, a comparison with former SIA forecasts indicates that they become more aggressive (that is more optimistic) with time.

While the development of silicon microelectronics in the past could be attributed mostly to the reduction of the feature size (progress in lithography), today it relies more on new material solutions, such as SOI, SON, SiGe or SiC. The combination of this trend with continuous miniaturization provides the opportunity of improving IC functionality and speed of operation.

Telecommunications and information technology are arguably the most powerful drivers behind microelectronics product development nowadays. Thus plenty of new applications are being created for fast analog and RF circuits, as well as for information processing ones. It is clear that with the anticipated  $f_{\rm max}=130$  GHz and  $f_T=65$  GHz to be reached by RF bipolar transistors in 2005, according to the 2001 issue of ITRS (it is interesting to note that in 1999 ITRS predicted only  $f_{\rm max}=50$  GHz and  $f_T=40$  GHz for 2005), a lot of effort must be put into the development of appropriate material, processing, characterization and modeling. Such an outstanding progress, however, will not happen without increased speed offered by new materials solutions. SiGe-base HBTs may serve as an example here – a device with  $f_T=350$  GHz has already been reported in the literature.

High-speed isn't, however, everything. Portable wireless products push, for obvious reasons, for low-power solutions. This trend requires new architectural solutions (e.g., channel thinning), and in consequence, new material, such as SOI (or its possible successor SON – silicon-on-nothing), where current driveability is considerably higher than in conventional MOSFETs.

In this issue the Reader will find the second part of the papers and lectures presented during the 6th Symposium Diagnostics & Yield: Advanced Silicon Devices and Technologies for ULSI Era, which took place in Museum of Earth, Warsaw, Poland on June 22–25, 2003. A number of the papers are devoted to the most important issues concerning semiconductor technology (challenges faced by CMOS technology, gate-dielectric fabrication, wafer-cleaning problems, fabrication of nanostructures, micromachined sensors) and advanced materials, such as SOI and SiGe. Several papers address the problems of characterization of semiconductor structures and nanostructures (DC and noise analysis, photoelectric measurements, scanning probe microscopy), as well as those of IC testing and assembly. The subject of modeling (both devices and circuits) and parameter extraction is covered, too.

We hope the Readers will find these Proceedings useful and interesting.

Organization of this Symposium would not be possible without the support of Polish Committee for Scientific Research (research projects no. 4T11B03523, 8T11B07519, 8T11B07419). The organizers acknowledge also the contribution of the Committee of Electronics and Telecommunications of Polish Academy of Sciences, and the NEXUS Microsystems Association. The organizers are also grateful to the National Institute of Telecommunications for making this journal available for the publication of the Symposium papers.

Andrzej Jakubowski – General Chairman Lidia Łukasiak – Programme Chairman Guest Editors Invited paper

# **Challenges in scaling of CMOS devices towards 65 nm node**

Małgorzata Jurczak, Anabela Veloso, Rita Rooyackers, Emmanuel Augendre, Sofie Mertens, Aude Rotschild, Marc Scaekers, Richard Lindsay, Anne Lauwers, Kirklen Henson, Simone Severi, Ivan Pollentier, and An de Keersgieter

Abstract—The current trend in scaling transistor gate length below 60 nm is posing great challenges both related to process technology and circuit/system design. From the process technology point of view it is becoming increasingly difficult to continue scaling in traditional way due to fundamental limitations like resolution, quantum effects or random fluctuations. In turn, this has an important impact on electrical device specifications especially leakage current and the circuit power dissipation.

Keywords—CMOS devices, gate dielectrics, shallow junctions, silicide, gate stack, lithography, gate patterning, silicon recess, device integration.

#### 1. Introduction

The traditional scaling approach, which has been the base of the semiconductor industry for the last 30 years is beginning to show the fundamental limits of the materials building the modules of a planar CMOS transistor. Significant efforts are being devoted to the introduction of new materials that will replace the existing ones to further extend the device scaling process.

However, even though the new materials and device architectures are being investigated, the gate length scaling below 60 nm has a significant impact on the electrical properties of the devices. The continuous thinning of the gate dielectric layers, the increasing channel doping and the aggressive, abrupt junctions, required to control the short channel effects, start to significantly affect circuit power dissipation.

Nitrided oxides, gate predoping, offset spacers, spike anneal, tilted pocket implants, ultra low energy implants are a few examples of the process steps that were introduced in the 0.13  $\mu$ m technology generation to enable device gate length scaling. These previous "improvements" will be able to prolong scaling down to 65 nm node. New solutions to device architecture, device substrate, gate stack will have to be introduced to maintain 12% increase in device performance forecasted by ITRS roadmap [1].

This paper gives an overview of the main challenges being faced in the front-end of line (FEOL) technology development for 65 nm node. This includes the gate stack, gate patterning, junction and silicide process.

#### 2. Gate stack

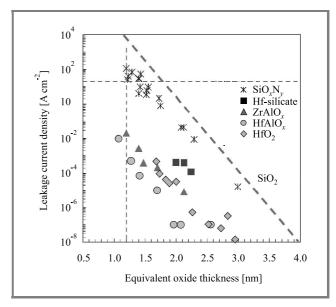

Aggressive scaling of CMOS devices puts severe constrains on the gate dielectric. In order to meet requirements for drive current and off-state leakage set up by ITRS roadmap it is essential to simultaneously scale further gate oxide thickness and limit the gate leakage current. In addition, mobility degradation has to be minimized and gate oxide reliability still has to meet the 10-year lifetime requirements. Despite low gate leakage current as compared to nitrided oxides (Fig. 1), high-*k* dielectrics are still not ready for device integration due to reliability problems, high mobility degradation and instability of the threshold voltage.

Fig. 1. Comparison of different gate dielectrics with respect to gate leakage and EOT.

Therefore, there is strong motivation to extend the use of oxynitrides to its ultimate limits. Oxynitrides fabricated with a new plasma nitridation techniques such as decoupled plasma nitridation (DPN) [2] or slot plane antenna (SPA) seem to be the best candidates for 65 nm high performance and general purpose CMOS devices (Fig. 1) at least until high-k materials reach their maturity for the gate dielectric applications. Using plasma nitridation it is possible to introduce more nitrogen than with furnace nitridation techniques into thin oxide layer and thus increase the dielectric constant k and scale equivalent oxide thickness without reducing significantly physical oxide thickness [3].

Continued thinning of gate dielectrics and an increase of the interface-state density created by plasma nitridation bring many concerns related to reliability issues. Thorough characterization shows, however, that a careful optimization of the gate dielectric process enables maintaining the maximal operation voltage, at which the device can be operational for 10 years, above the supply voltage [4]. This is possible since oxide reliability is dependent rather on physical oxide thickness than on EOT.

The gate activation, which has direct impact on the drive current, is more and more affected by the reduced thermal budged required in order to control short channel effects. Additional gate implantation called gate predoping is mandatory to maintain low gate depletion. Metal gate seems to be a solution to this problem, however, due to the unsuitability of the work function and highly complex integrity it will not be ready for the 65 nm node.

#### 3. Gate patterning

In order to cope with progressive scaling of CMOS devices new lithography techniques are being investigated. The 157 nm lithography is considered as the leading candidate for semiconductor device manufacturing at the 65 nm technology node [5]. However, development of 157 nm lithography requires considerable effort and effective solutions to resist and reticle materials, lenses, CD metrology, etc. This list of challenges raises fears that the 157 nm lithography will not be ready for the 65 nm node. Therefore, other methods such as resist or hard mask trimming were developed to support lithography in the scaling progress.

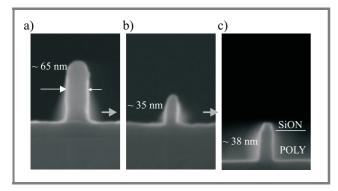

In the 65 nm node, where the gate length is in the range of 65–25 nm, depending on applications, the key process step developments are lithography, dry etch, and CD metrology. With respect to lithography, the emphasis is put on the development of thin resist processes (using 193 nm lithography) in combination with alternating phase shift mask (AltPSM) optical extensions. With this combination the lines down to 65 nm with good CD control can be printed (Fig. 2a). Further reduction of the gate length is obtained by subsequent resist or hard mask trim-

Fig. 2. Visualization of the trim and gate etch: (a) showing the X-section of features after litho; (b) etch trim; (c) gate etch and strip.

ming (Fig. 2b). Trimming techniques allow obtaining gate lengths down to a few nanometers.

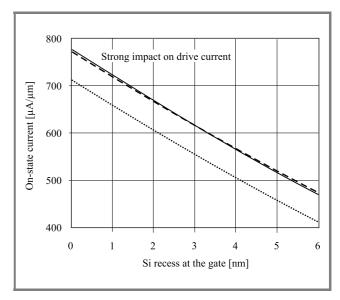

Fig. 3. Impact of Si recess created at the gate patterning on the drive current (simulation results).

An important issue when scaling devices and the gate oxide thickness is silicon recess in source and drain areas which occurs during overetch step in gate electrode patterning. Even small, a few nanometers consumption of Si in the substrate has considerable impact on device performance and leads to increase in the off-state leakage and series resistance (Fig. 3).

#### 4. Junction

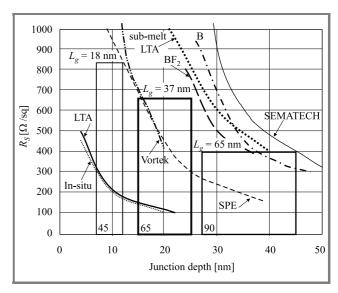

Approaching the 65 nm node ITRS requirements for ultrashallow junctions (USJ) has become a great challenge, es-

*Fig. 4.* Summary of p<sup>+</sup>/n junctions obtained with different techniques. The boxes indicate the requirements for different technology generations (literature results).

1/2005

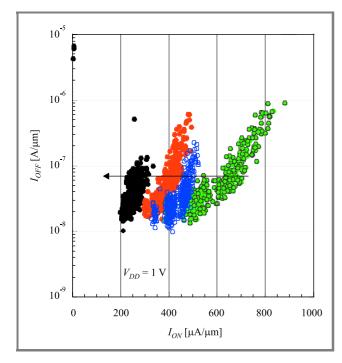

Fig. 5. Drive current versus off-state leakage for NMOS devices with different doses in extensions. The arrow indicates the reduction in the doping concentration in the junctions.

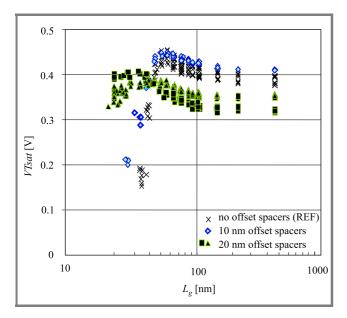

Fig. 6. Impact of offset spacers on control of short channel effects.

pecially for p<sup>+</sup> dopants. With boron, traditionally used for p<sup>+</sup>/n junction formation, implanted alone and annealed with conventional methods, the 90 nm node specifications can hardly be reached (Fig. 4). Simple lowering of implantation dose reduces the junction depth but on the other hand leads to high series resistance and degradation of the on-state current (Fig. 5). The literature data shows that only with very sharp spike anneal (high rump-up and rump down using, e.g., Levitor or Vortek tool) the improvement in the trade-

off between junction resistance and junction depth can be achieved [6]. Even better results can be obtained with a co-implantation with other elements and/or pre-amorphization implants in conjunction with spike anneal. The combination of Ge pre-amorphization, F co-implantations and fast rampup spike anneal appeared to be sufficient to fulfill the 65 nm node requirements [7]. For the next generation other alternative routes of forming the junctions such as solid phase epitaxial re-growth (SPER) [8] or laser anneal (LTA) are investigated.

Introduction of offset spacers allows relaxing the requirements for the extensions without aggravating short channel effects (Fig. 6). This, however, puts very severe constrains on their width control since any small variations in the spacer width may result in huge variation in VT and offstate leakage.

#### 5. Silicide

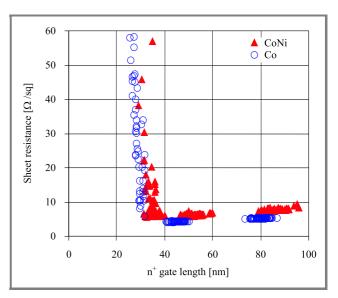

The scaling of the gate length (below 40 nm) goes in parallel with the reduction in the HDD junction depth. Shallower junctions, in turn, determine more constrained requirements for the silicides. Conventionally used CoSi seems to reach its ultimate limits. For the gate length below 40 nm gate sheet resistance increases dramatically (Fig. 7), which is related to silicide instability and silicide cracking. No improvement is observed when Co is alloyed with Ni. Besides, high Si consumption during the silicide process leads to unacceptable increase in the junction leakage. Therefore, other materials such as NiSi or PtSi were considered as potential candidates for 65 nm technology node [9].

Fig. 7. Gate sheet resistance of Co and CoNi silicided gate as a function of the gate length.

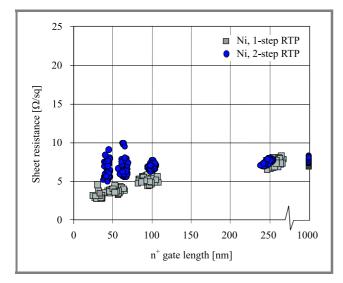

For Ni-silicided poly gates low sheet resistance is obtained down to the narrowest line widths (Fig. 8). The trade-off between junction leakage and silicide sheet resistance is

Fig. 8. Gate sheet resistance of Ni silicided gate processed with different annealing steps as a function of the gate length.

in favour of Ni-silicide. Besides, NiSi is known to have smaller contact resistance, which has significant role in total resistance of the junctions in sub-50 nm devices.

#### 6. Conclusions

Conventional bulk scaling reaches its physical limitations. The 65 nm CMOS appears to be the last technology node, where the conventional planar transistor architecture in conjunction with standard modules will be applied. In order to maintain the trend in performance improvement, next technology generations will probably have to deal with more exotic solutions such as strained silicon, metal gate integration, high-*k* dielectrics (mainly for low power applications) and eventually double gate architectures.

#### References

- International Technology Roadmap for Semiconductions, 2001, http://public.itrs.net/Files/2001ITRS/Home.htm

- [2] F. N. Cubaynes, J. Schmitz, C. van der Marel, H. Snijders, A. Veloso, and A. Rothschild, "Plasma nitridation optimization for sub-1 A gate dielectrics", in *ECS Symp.*, Paris, France, 2003.

- [3] A. Veloso, F. N. Cubaynes, A. Rothschild, S. Mertens, R. De-graeve, R. O'Connor, C. Olsen, L. Date, M. Schaekers, C. Dachs, and M. Jurczak, "Ultra-thin oxynitride gate dielectrics by pulsed-RF DPN for 65 nm general purpose CMOS applications", in *Conf. ESSDERC'03*, Lisbon, Portugal, 2003.

- [4] R. O'Connor, R. Degraeve, B. Kaczer, A. Veloso, G. Hughes, and G. Groeseneken, "Weilbull slope and voltage acceleration of ultra-thin (1.1–1.45 nm EOT) oxynitrides", in *Conf. INFOS'03*, Stará Lesná, Slovakia, 2003.

- [5] L. Van den Hove, M. Goethals, K. Ronse, M. Van Bavel, and G. Vandenberghe, "Lithography for sub-90 nm applications", in *IEDM Tech. Dig.*, San Francisco, USA, 2002, pp. 3–8.

- [6] R. Lindsay, B. Pawlak, J. Kittl, K. Henson, C. Torregiani, S. Giangrandi, R. Surdeanu, W. Vandervorst, A. Mayur, J. Ross, S. McCoy, J. Gelpey, P. Stolk, and K. Maex, "A comparison of spike, flash, SPER and laser annealing for 45 nm CMOS", in *MRS Symp.*, Paris, France, 2003.

- [7] B. J. Pawlak, R. Lindsay, R. Surdeanu, X. Pages, W. Vandervorst, and K. V. D. Jeugd, "The role of F with Ge pre-amorphisation in forming PMOS junctions for the 65 nm CMOS technology node", in ECS Symp., Paris, France, 2003.

- [8] R. Lindsay, B. J. Pawlak, J. Kittl, K. Henson, S. Giangrandi, R. Duffy, R. Surdeanu, W. Vandervorst, P. Stolk, and K. Maex, "Leakage optimisation of ultra-shallow junctions formed by solid phase epitaxial regrowth (SPER)", *Proc. J. Vac. Sci. Technol*, vol. B, Febr. 2003.

- [9] A. Lauwers, J. Kittl, A. Akheyar, M. Van Dal, O. Chamirian, M. de Potter, R. Lindsay, and K. Maex, "Silicide scaling: Co, Ni or CoNi?", in ECS Symp., Paris, France, 2003.

Małgorzata Jurczak received M.Sc. and Ph.D. degrees in electrical engineering from the Warsaw University of Technology (WUT), Poland, in 1991 and 1997. In 1991 she joined WUT, where she worked on modelling of MOS SOI devices. In 1994 she was with NMRC, Cork, Ireland, and in 1997 with Kyung Hee University, Seoul,

Korea. In 1998 she joined CNET Grenoble, France Telecom. She was involved in development of 0.18 and 0.12  $\mu$ m CMOS process and alternative approaches for sub-0.1  $\mu$ m CMOS. In 2000 she joined IMEC, Leuven, Belgium. In the years 200-2003 she was the IMEC coordinator of the JDP program with Philips on device process integration for 90 nm and 65 nm CMOS. From 2003 she has been the group leader of the CMOS Device Implementation Projects (45 nm CMOS, FUSI gate, strained Si, HK+MG integration, FD SOI, MUGFET). She is also a project manager of IMEC Industrial Affiliation Program (IIAP) on ultimate devices EMERALD. She has participated in several European projects: ACE, ULTRA, MEDEA, HUNT. She was the project coordinator of the European IST ARTEMIS project. Currently she is in the Technical Advisory Committee of the IST Integrated Project NanoCMOS. She holds 15 French and American patents and authored and co-authoured more than 60 papers. She has been a member of scientific committee of IEDM (in 2002 and 2003) and ESSDERC conferences (2000, 2004 and 2005). She received the Best Paper Award at ESSDERC'2000 Conference and the Paul Rappaport Award for the best paper published in IEEE TED

e-mail: malgorzata.jurczak@imec.be IMEC Kapeldreef st 75

1/2005

Anabela Veloso, Rita Rooyackers, Emmanuel Augendre, Sofie Mertens, Aude Rotschild, Marc Scaekers, Richard Lindsay, Anne Lauwers, Kirklen Henson, Simone Severi, Ivan Pollentier, An de Keersgieter IMEC

Kapeldreef st 75 3001 Leuven, Belgium

3001 Leuven, Belgium

Invited paper

# Gate dielectrics: process integration issues and electrical properties

Udo Schwalke

Abstract—In this work we report on the process integration of crystalline praseodymium oxide  $(Pr_2O_3)$  high-k gate dielectric. Key process steps that are compatible with the high-k material have been developed and were applied for realisation of MOS structures. For the first time  $Pr_2O_3$  has been integrated successfully in a conventional MOS process with  $\mathbf{n}^+$  polysilicon gate electrode. The electrical properties of  $Pr_2O_3$  MOS capacitors are presented and discussed.

Keywords—high-k dielectrics, CMOS, Pr<sub>2</sub>O<sub>3</sub>, process integration, resist removal, wet chemical cleaning, wet chemical etching, RIE.

#### 1. Introduction

The scaling of gate dielectric thickness is a major challenge for future ULSI CMOS technologies. Only by taking advantage of in-situ gate stack processing and advanced CMOS process architectures, excellent CMOS device characteristics could be achieved with ultra-thin (1.6 nm) SiO<sub>2</sub> gate dielectric [1]. However, the gate oxide thickness has to be scaled down aggressively much further into the sub-1 nm regime within the next decade, according to the ITRS roadmap [2]. At such a thickness, unacceptably high direct tunneling leakage current will flow through the gate oxide. The exponential increase in tunneling current with decreasing film thickness represents a fundamental scaling limit for SiO<sub>2</sub>. In order to overcome this barrier, the use of alternative gate dielectrics with a higher permittivity (high-k) is urgently needed. Due to the high-k values, gate dielectrics with sub-1 nm equivalent oxide thickness can be realised and show acceptable low leakage currents. Unfortunately, most of these amorphous materials are not sufficiently stable [3], change phase [4] and electrical properties at temperatures much lower than required for CMOS processing. Accordingly, the most desirable direct substitution of SiO2 in a given CMOS process is not

Very recently it was shown that crystalline praseodymium oxide (Pr<sub>2</sub>O<sub>3</sub>) films have excellent dielectric properties [5]. Besides an effective dielectric constant of  $K_{Pr_2O_3}\approx 30$  and low leakage currents (<  $10^{-8}$  A/cm² @ 1 V & EOT= 1.4 nm), Pr<sub>2</sub>O<sub>3</sub> films were found to be thermally stable up to  $1000^{\circ}C$  for 15 s RTA anneals in N<sub>2</sub> ambient. Because of these attractive properties, Pr<sub>2</sub>O<sub>3</sub> appear as a suitable high-*k* replacement for SiO<sub>2</sub>.

Although these first results are very promising, a successful CMOS process integration of crystalline high-k Pr<sub>2</sub>O<sub>3</sub> gate dielectric requires a substantial amount of process development. Besides thermal processing, especially wet chemical etching and cleaning procedures as well as reactive ion etching (RIE), processes compatible with the new material have to be developed. In addition, process-damage effects on the high-k dielectric needs to be evaluated and minimised. In this work we report on a successful attempt to integrate Pr<sub>2</sub>O<sub>3</sub> directly into a given n<sup>+</sup> polySi gate MOS technology. The electrical properties of the MOS devices are presented and will be discussed.

# 2. Praseodymium oxide growth and wafer preparation

For the process integration experiments  $Pr_2O_3$  was grown on hydrogen terminated 3" Si(100) wafers in a multichamber molecular beam epitaxy (MBE) system [5]. The MBE is equipped with e-beam evaporators for Si and praseodymium oxide. Pr<sub>2</sub>O<sub>3</sub> layers were grown on preimplanted p-type Si(100) wafers at temperatures between 625 and 725°C using a commercially available ceramic Pr<sub>6</sub>O<sub>11</sub> source. The layers were subsequently covered insitu with 50 nm undoped polySi, since unprotected Pr<sub>2</sub>O<sub>3</sub> layers are not stable against air [6]. The polySi protected Pr<sub>2</sub>O<sub>3</sub> wafers were transferred to the CMOS process fab of the Institut für Halbleitertechnik (IHT) at the Technische Universität Darmstadt for process development. After RCA clean and a brief HF-dip a 250 nm in-situ phosphorous doped polySi layer was deposited at approximately 750°C. The structures obtained in this way were mainly used for subsequent process development.

#### 3. Development of key process steps

#### 3.1. Wet chemical cleaning and etching

Wet chemical processing is extensively used in CMOS manufacturing, for cleaning, etching and resist removal. However, little is known on the compatibility of these standard procedures with high-k materials, especially  $Pr_2O_3$ . In order to obtain first-hand information, blanket  $Pr_2O_3$  test samples were subjected to various wet chemical treatments. The results of wet chemical cleaning and etching

studies are summarized in Table 1. Pr<sub>2</sub>O<sub>3</sub> remains stable in DI-water, HF-dip and the alkaline component of the RCA clean, and no change in the film thickness was observed by means of ellipsometry. However, Pr<sub>2</sub>O<sub>3</sub> was found to dissolve in the standard RCA clean and appears unstable

Table 1 Wet chemical cleaning and etching

| Procedure                          | Effect on Pr <sub>2</sub> O <sub>3</sub> |  |

|------------------------------------|------------------------------------------|--|

| HF-dip                             | Appears stable                           |  |

| Buffered HF                        | Unstable                                 |  |

| RCA clean                          | Soluble                                  |  |

| RCA clean, alkaline component only | Stable                                   |  |

| H <sub>3</sub> PO <sub>4</sub>     | Soluble                                  |  |

| HCl                                | Soluble                                  |  |

| DI-water                           | Stable                                   |  |

in buffered HF solution. HCl solution of 0.75% was found to etch  $Pr_2O_3$  with a high etch rate of 28 nm/min. Obviously, acid containing solutions, in particular HCl, are suitable to remove  $Pr_2O_3$  films selectively from the silicon surface.

#### 3.2. Resist removal

Resists used for lithography have to be removed after etching or ion implantation. However, several wet chemical methods for resist removal contain acids and are, therefore, expected to dissolve  $Pr_2O_3$ . In fact, such a behavior was observed as summarized in Table 2. Only organic solvents, like acetone or AZ100 remover, are suitable for resist stripping when  $Pr_2O_3$  films are present.

Table 2 Resist removal

| Procedure                                                     | Effect on Pr <sub>2</sub> O <sub>3</sub> |  |

|---------------------------------------------------------------|------------------------------------------|--|

| Acetone                                                       | Stable                                   |  |

| H <sub>2</sub> SO <sub>4</sub> /H <sub>2</sub> O <sub>2</sub> | Soluble                                  |  |

| HNO <sub>3</sub> (100%)                                       | Soluble                                  |  |

| AZ100 wet remover                                             | Stable                                   |  |

| O <sub>2</sub> -plasma ashing                                 | Change in film properties                |  |

Besides wet chemical treatments, resist ashing in  $O_2$  plasma is a commonly used procedure. A clear change in film properties was observed after  $O_2$  plasma treatment, especially the etch rate in buffered HF was found to increase compared to  $Pr_2O_3$  reference samples. Most likely oxygen radicals produced in the plasma are incorporated in the praseodymium oxide film and/or may diffuse through and react with the Si-interface. In order to obtain further information we deposited aluminum dots on these samples and performed CV measurements. We observed a reduction in the dielectric constant and an increase in the threshold voltage. Both results suggest that an interfacial oxide is formed

as a result of the  $O_2$  plasma treatment, similar to the film degradation of unprotected  $Pr_2O_3$  when exposed to air for sufficiently long times [6].

#### 3.3. Anisotropic reactive ion etching

The development of a highly selective RIE process is another major issue for a successful process integration of praseodymium oxide in the polySi gate CMOS process. In order to avoid damaging of the silicon substrate, the polySi gate etch has to stop at the dielectric. We found that our standard  $SF_6/Cl_2$  process fulfills these requirements. The selectivity of the polySi-RIE against  $Pr_2O_3$  is higher than 300 so that the process window is sufficiently large to allow for the necessary over-etching.

#### 4. Results and discussion

#### 4.1. Process integration of $Pr_2O_3$

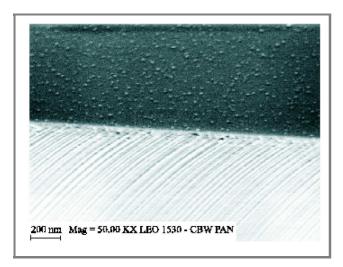

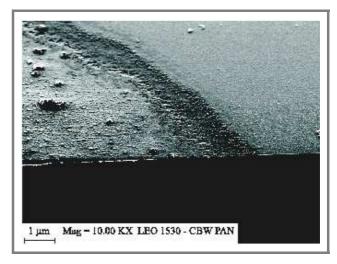

After the appropriate RCA clean and a brief HF-dip a 250 nm in-situ phosphorus doped polySi layer was deposited on the 50 nm polySi-covered  $Pr_2O_3$  wafers at approximately 750°C. Subsequently, the standard lithography was applied using the gate mask. The  $n^+$  polySi gate stack is defined by anisotropic reactive ion etch using  $SF_6/Cl_2$ .

Fig. 1. Microscope image of n<sup>+</sup> polySi/Pr<sub>2</sub>O<sub>3</sub> gate test structures after RIE. The inset shows an enlarged part of a meander structure.

In Fig. 1 a part of the test chip at the gate level is shown after the polySi gate etch. The inset in Fig. 1 shows an enlargement of a polySi meander, which is well defined. No polySi residues or damage to the  $Pr_2O_3$  dielectric in the open areas has been observed. Also, within the uncertainty of the thickness measurements no thinning of

the praseodymium oxide was detected, confirming the high selectivity of the RIE process.

#### 4.2. HF-CV characteristics

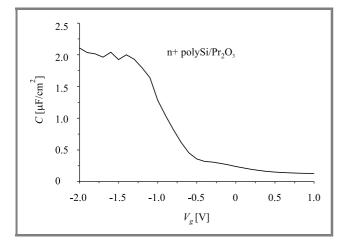

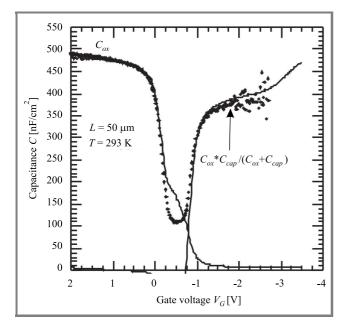

After wet resist strip and cleaning, the gate stack was briefly annealed at  $900^{\circ}$ C, 10 s in  $N_2$  using RTA in order to activate the gate doping. Subsequently, electrical measurements on  $n^+$  polySi/Pr<sub>2</sub>O<sub>3</sub>/Si capacitors were performed. In Fig. 2 an example of the HF-CV characteristic is shown.

Fig. 2. HF-CV curve measured at 10 kHz to minimise serial resistance effects.

No evidence for hysteresis effects was noted when changing polarity of the sweep voltage within this bias range. From the accumulation capacitance of the HF-CV curves the effective dielectric constant was calculated  $K_{\rm Pr_2O_3}=36$ , using the physical film thickness values measured by ellipsometry. The corresponding equivalent oxide thickness EOT =  $d_{\rm Film}*(K_{\rm SiO_2}/K_{\rm Pr_2O_3})$  was determined as EOT = 1.8 nm, in this case without QM corrections.

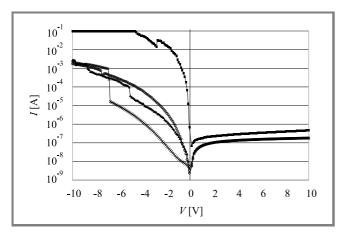

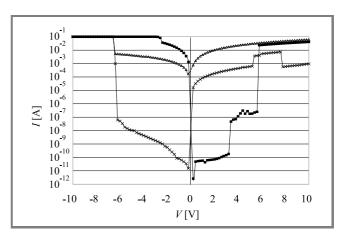

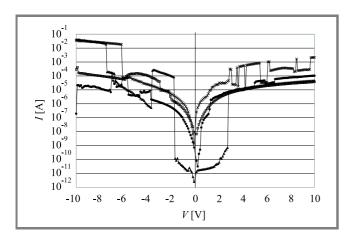

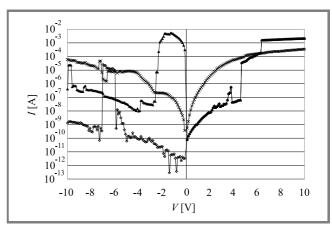

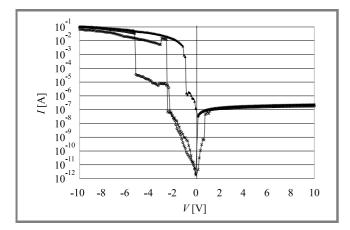

#### 4.3. Leakage characteristics

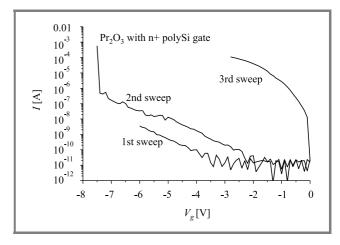

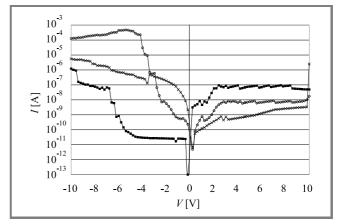

In Fig. 3 an example of the current-voltage characteristics is shown. For gate voltages below |-3| V, which correspond to an equivalent field strength of approximately 22 MV/cm, the measured leakage currents are around 10 pA, which is given by the detection limit of the measurement system. The upper limit of the current density in this bias range is estimated to be  $\approx 10^{-6} \text{ A/cm}^2$ , in good agreement with previous results on simple gold-dot capacitors [5]. For further increased gate bias, a tunneling current starts to appear. Directly after the first sweep, a second sweep was performed. As evident from the shift in the I-V characteristics, significant charge trapping has occurred. The dielectric breakdown takes place at a gate bias of |-7.5| V, which corresponds to a breakdown field of approximately 41 MV/cm, also in agreement with previous observations of gold-dot capacitors. However, in contrast

*Fig. 3.* Example of the current-voltage characteristics of the  $n^+$  polySi/Pr<sub>2</sub>O<sub>3</sub> MOS capacitors.

to previous findings, the breakdown was found irreversible, as evident from the 3rd sweep shown in Fig. 3.

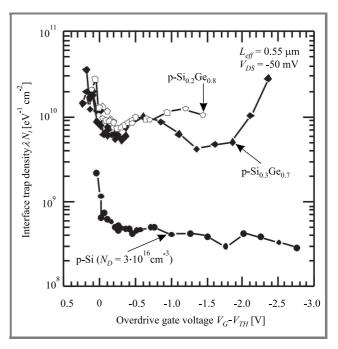

#### 4.4. Interface trap density and oxide charge

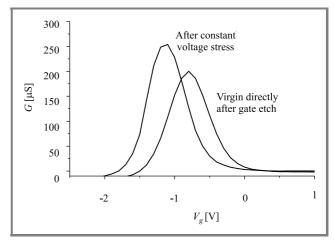

Admittance measurements were performed to obtain the equivalent parallel conductance G that can be used to get information on the interface trap density  $D_{it}$ . For the virgin MOS capacitor a value of  $D_{it} = 3.5 \cdot 10^{11}$  /cm² eV is deduced from the peak conductance shown in Fig. 4. Compared to high quality device-grade SiO<sub>2</sub> gate oxides, this value corresponds to an increase of at least 2 orders of magnitude and is expected to degrade MOSFET device characteristics. Clearly, a substantial amount of interface engineering and optimization is needed in order to achieve the same quality level as for SiO<sub>2</sub>.

Fig. 4. Results of conductance measurements performed on virgin and electrically stressed devices.

When the  $Pr_2O_3$  capacitor was stressed with 35 MV/cm for 10 s, an increase in interface trap density to  $D_{it} = 6 \cdot 10^{11}$  /cm<sup>2</sup> eV was observed (Fig. 4). In addition, the peak position is shifted to further negative values, indicating

the build-up of positive trapped charge on the order of  $4\cdot 10^{12}$  q/cm<sup>2</sup>. In this respect, the Pr<sub>2</sub>O<sub>3</sub> dielectric behaves similarly to SiO<sub>2</sub>, although the detailed mechanisms are probably quite different and require further investigation.

#### 5. Conclusion

The crystalline high-k Pr<sub>2</sub>O<sub>3</sub> material was found to be compatible with n<sup>+</sup> polySi gate CMOS processing when appropriate etching and cleaning procedures are used and thermal processing is restricted to RTA. We therefore conclude that a complete re-engineering of the CMOS manufacturing process may not be necessary in this case. However, the electrical characteristics of the Pr<sub>2</sub>O<sub>3</sub> MOS structures reveal very high values of the interface trap density. Clearly, a substantial amount of interface engineering and optimization is needed in order to achieve the same quality level of state-of-the-art device-grade SiO<sub>2</sub>. This is especially important in view of the fact that an enormous knowledge exists about the SiO<sub>2</sub>/Si system used and continuously optimised in semiconductor manufacturing for more than 30 years.

#### References

- U. Schwalke, A. Gschwandtner, G. Innertsberger, and M. Keber, "Through-the-gate-implanted ultrathin gate oxide MOSFETs with corner parasitics-free shallow-trench-isolation", *IEEE EDL*, vol. 20, no. 7, 1999, p. 363.

- [2] The International Technology Roadmap for Semiconductor, Semiconductor Industry Association, 1999, http://public.itrs.net/Files/2003ITRS/Home2003.htm

- [3] A. Kerber, E. Cartier, R. Degraeve, L. Pantisano, Ph. Roussel, and G. Groeseneken, "Strong correlation between dielectric reliability and charge trapping in SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate stacks with TiN electrodes", in VLSI Symp. Technol., Honolulu, USA, 2002.

- [4] P. J. Chen, E. Cartier, R. J. Carter, T. Kauerauf, C. Zhao, J. Petry, V. Cosnier, Z. Xu, A. Kerber, W. Tsai, E. Young, S. Kubicek, M. Caymax, W. Vandervorst, S. De Gendt, M. Heyns, M. Copel, P. Bajolet, and J. Maes, "Thermal stability and scalability of Zraluminate-based high-k gate stacks", in VLSI Symp. Technol., Honolulu, USA, 2002.

- [5] H. J. Osten, J. P. Liu, P. Gaworzewski, E. Bugiel, and P. Zaumseil, "High-k gate dielectrics with ultra-low leakage current based on praseodymium oxide", *Tech. Dig. IEDM*, 2000, pp. 653–656.

- [6] H. J. Osten, E. Bugiel, J. Dąbrowski, A. Fissel, T. Guminskaya, J. P. Liu, H. J. Müssig, and P. Zaumseil, "Epitaxial praseodymium oxide: a new high-k dielectric", in *Proc. Int. Worksh. Gate Insulat.*, Tokyo, Japan, 2001, pp. 100–103.

Udo Schwalke was awarded a Research Fellowship from the Alexander-von-Humboldt-Foundation for his Ph.D. thesis in 1984. During 1984–1986, he was appointed Caltech Research Fellow at the California Institute of Technology, USA. In 1987, he joined the Siemens AG, R&D Microelectronics in Munich, Germany.

From 1990–1992 he was responsible for the 64 Mb DRAM device design at IBM/Siemens, USA. Subsequently, at Infineon Technologies AG (the former Siemens Semiconductor Group) he worked on novel process architectures and device reliability issues. Since August 2001, Dr. Schwalke is Professor in electrical engineering and the Managing Director of the Institute of Semiconductor Technology at the Technical University of Darmstadt. He has authored and co-authored more than 60 papers, holds several patents and is a member of IEEE and ECS.

e-mail: schwalke@iht.tu-darmstadt.de Institut für Halbleitertechnik (IHT) Technische Universität Darmstadt Schlossgartenstr. 8 64289 Darmstadt, Germany Invited paper

# **Understanding of wet** and alternative particle removal processes in microelectronics: theoretical capabilities and limitations

François Tardif, Adrien Danel, and Olivier Raccurt

Abstract—A 2 orders of magnitude range of van der Waals interactions is considered here to take the majority of the variety of shapes and materials of actual particles into account. Comparing these interactions with the repulsive forces generated by electrostatic charges, drag, surface tension, shock waves, high accelerations and aerosol particles, the intrinsic capabilities and limitations of the different cleaning processes can be predicted. Three kinds of particle-removal processes have been identified - universal processes capable of removing all particle sizes and types, even from patterned wafers, processes that present the same theoretical ability but are actually limited by the accessibility of the particles, and finally cleanings that are not able to remove all particle sizes.

Keywords—cleaning, SC1, particle removal.

#### 1. Introduction

The continuous increase of IC integration density requires a reduction of both device dimensions and the corresponding amount of the material used. Consequently, the concentration of contaminants affecting the fabrication yield of very competitive microelectronic manufacturing is becoming smaller and smaller. Therefore, cleaning performance has to be continuously improved to remove the ultimate traces of contamination, such as particles, metals, organics, bases and anions.

According to the International Technology Roadmap for Semiconductors [1], smaller and smaller particle sizes will have to be eliminated as the device dimensions decrease: 50 nm as from 2004 and 10 nm in 2016.

Particles will probably be the most challenging type of contamination in the near future as the removal mechanism in the conventional Standard Clean 1 (SC1) [2] process is mainly based on a controlled consumption of the layer under the particle. But this consumption will be rapidly prohibited as the accuracy of the device dimensions (implantation, silicon on insulator, etc.) are now approaching the under-etching thicknesses required for particle removal.

In this work, fundamental particle-substrate interactions due to van der Waals, drag and surface tension forces, as well as electrostatic charges, are used to understand the intrinsic capabilities and limitations of the wet SC1 process and emerging new techniques such as explosive evaporation, high velocity sprays, acoustic waves, laser and cryogenic techniques.

#### 2. Forces acting on particles

The main forces likely to be exerted on fine particles are calculated in Table 1. It can be seen from this table that the main four parameters that drive the particle adhesion/removal mechanisms are the electrostatic, van der Waals, capillary and drag forces [3].

Table 1 Orders of magnitude of the different forces acting on a 100 nm spherical particle in a solution with the density of 1

| Forces          | Order of magnitude | Proportionality |

|-----------------|--------------------|-----------------|

|                 | (N)                | (R: Radius)     |

| Van der Waals   | $10^{-7}$          | R               |

| Electrostatic   | $10^{-8}$          | _               |

| Capillary       | $10^{-8}$          | R               |

| Drag            | $10^{-9}$          | R               |

| (water, 10 m/s) | 10                 | IX.             |

| Gravitation     | $10^{-16}$         | $R^3$           |

| Archimedes      | $10^{-17}$         | $R^3$           |

| Hydrostatic     | $10^{-21}$         | $R^3$           |

#### 2.1. Capillary forces

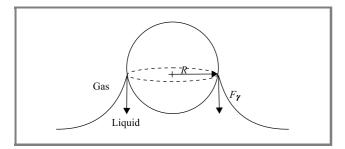

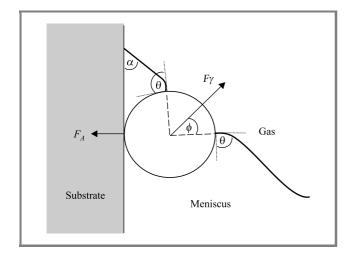

The surface tension  $\gamma_{lg}$  is due to the cohesion between the molecules of the media and tends to minimize the interfacial areas. It represents a force per unit of interfacial length. In the case of the reference spherical particle, the maximum capillary force is obtained when the liquid wets the particle material perfectly and the gas/liquid interface is acting on the whole particle perimeter (see Fig. 1):

$$F_{\gamma} = 2\pi R \gamma_{l_{\varphi}}. \tag{1}$$

Fig. 1. Schematic of the maximum capillary force acting on a particle at a liquid/gas interface (case of contact angle = 0).

#### 2.2. Drag forces

The viscosity of the moving fluids induces a drag force on the particles. In the case of a spherical particle of diameter D placed in a flow velocity  $V_p$ , this force is given with a good approximation [4] by the Stokes law up to the Reynolds number of ten<sup>1</sup>. In the case of a particle deposited on a surface, an additional constant of 1.7 accounting for the effect of the surface must be added [5]:

$$F_{Drag} = 1.7 \cdot 3\pi \,\mu \,DV_p \,, \tag{2}$$

where  $\mu$  represents the fluid viscosity:  $10^{-3}$  kg/m·s for water at  $20^{\circ}$ C.

This force is theoretically able only to push the particle in parallel to the surface. It can be expected that an asperity on the particle or on the substrate will transform this tangential force to a lift-off momentum [6]. In the case of non-spherical particles, the drag forces are generally higher.

#### 2.3. Van der Waals forces

The particle-substrate attractions due to the van der Waals forces result from the dipole/dipole interactions between their constitutive molecules. These forces are so high that the particles are generally flattened on the substrate. The integration of the interactions between all the constitutive volume elements of a spherical particle or an infinite flat particle both on a perfectly flat substrate are given by (3) and (4), respectively:

$$F_{vdW} = \frac{AR}{6h^2},\tag{3}$$

$$F_{vdW} = \frac{AS}{6\pi h^3},\tag{4}$$

where: R – particle radius, h – particle-substrate distance (the minimum distance equal to the Lennard-Jones distance of  $h_0 = 0.4$  nm for the considered materials),

A – the Hamaker constant (depends on the particle, substrate materials and on the nature of the media: interaction transmission), S – facing particle and substrate surface.

The Hamaker constants for different particle/substrate materials can be calculated using the data and the formula given by Israelachvili [7]. The results listed in Table 2 show that van der Waals forces for typical particle materials on  $SiO_2$  substrates can vary by one order of magnitude depending on the media.

Table 2

Hamaker constants in water and in air calculated from reference [7]

| Media | Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> | SiO <sub>2</sub> /SiO <sub>2</sub> | PSL/SiO <sub>2</sub>           |

|-------|--------------------------------------------------|------------------------------------|--------------------------------|

| Water | $1.6 \cdot 10^{-20} \text{ J}$                   | $6.5 \cdot 10^{-21} \text{ J}$     | $1.0 \cdot 10^{-20} \text{ J}$ |

| Air   | $9.6 \cdot 10^{-20} \text{ J}$                   | $6.3 \cdot 10^{-20} \text{ J}$     | $7.5 \cdot 10^{-20} \text{ J}$ |

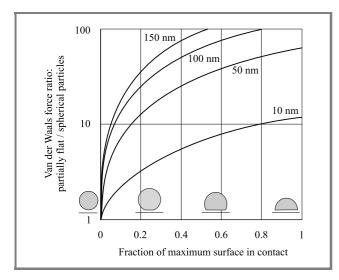

The difference between van der Waals attractions acting on the reference rigid and spherical particle and on actual particles is investigated here. The consequence of the non ideality of the actual particles: flattening, non specific shape, roughness, partially embedded, etc., can finally be considered as an additional flat surface in contact with the substrate.

In this work, the difference between the ideal and rigid sphere and the actual non-ideal particle is arbitrarily expressed by the fraction f equal to the surface in contact divided by the maximum surface that a particle of the same dimension is able to present  $\pi R^2$ :

$$f = \frac{S}{\pi R^2} \,. \tag{5}$$

In this way, f is null for an ideal particle and reaches 1 for a particle presenting the maximum surface in contact.

For a quasi-spherical particle presenting a small flat contact area, the total van der Waals forces can be considered as the sum of the contributions from the non-deformed particle and the contact surface [8] with the latter dominating the contribution from the spherical particle. Therefore, the ratio  $\mathfrak R$  between the van der Waals attraction of the actual and the ideal (rigid and spherical) particles can be approximated by the equation:

$$\Re = \frac{\frac{AR}{6h^2} + \frac{AS}{6\pi h^3}}{\frac{AR}{6h^2}} = 1 + f\frac{R}{h}.$$

(6)

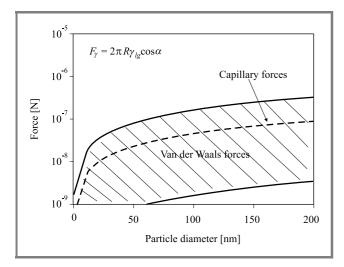

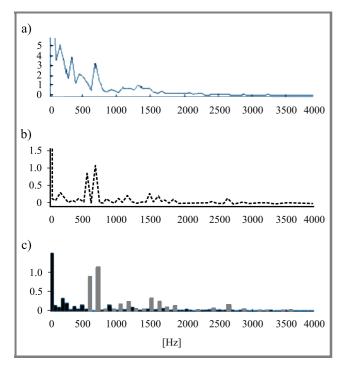

The results have been plotted in Fig. 2 for particle sizes ranging from 10 to 150 nm. It can be seen that the van der Waals forces increase rapidly with the non-ideality of the particles and can be more than 2 orders of magnitude higher than those for the ideal particle. This effect decreases with the particle size. Finally, due to a large variation range

<sup>&</sup>lt;sup>1</sup>For a 100 nm particle, the Reynolds number of 10 corresponds to a water flow velocity of 100 m/s!

of the Hamaker constant and considerable impact of the particle, van der Waals interactions can vary to a very large extent for the different existing particle types.

Fig. 2. Ratio  $\mathfrak{R}$  between van der Waals forces calculated for the reference rigid sphere and particles presenting a flat surface in contact. This surface is given in percentage of the area of the sphere cross section which represents the maximum contact surface for a given particle size.

In this work, we arbitrarily chose to consider the van der Waals forces present in the system consisting of a rigid sphere of  $Al_2O_3$  on  $SiO_2$  substrate because its Hamaker constant is the highest of those listed in Table 2. In order to account for a shift from ideality, a range of the Hamaker constants of up to 2 orders of magnitude above the value mentioned above is considered. This approach enables a very wide majority of actually observed particles to be covered but clearly does not take into account the extreme cases of flat-shape particles made of materials exhibiting very high Hamaker constants.

The substrate roughness is not considered here as it generally decreases the contact areas leading to lower van der Waals interactions.

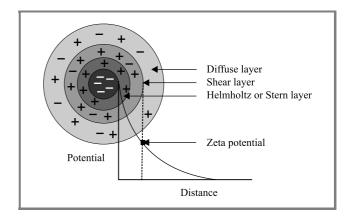

#### 2.4. Force originating from electrostatic charges

Material surfaces usually present electrostatic charges that originate from ionization or dissociation of functional surface groups in chemical equilibrium with  $H^+$  ions from the media (pH). In a liquid, a large number of charges are available close to the surface<sup>2</sup>. Ions carrying charge of the sign opposite to that of the surface (the counter ions) are immediately attracted to the surface, masking its surface potential until apparent neutrality is reached. As shown in Fig. 3, the surface charge density is characterized by the Zeta potential. This potential is due to the contributions from the particle charges and the retinue of counter ions

sufficiently attached to the particle surface when it moves against the liquid (shear layer), e.g., under the influence of an electric field.

The thickness of the diffuse layer results from the competition between the electrostatic attraction exerted on the counter ions that build up at the charged surface and their re-diffusion to the bulk solution. A high temperature and a low ionic strength, therefore, enhance the diffuse layer thickness.

Fig. 3. Representation of a negatively charged particle dipped in an electrolyte.

Fig. 4. Representation of a negative particle dipped in an electrolyte.

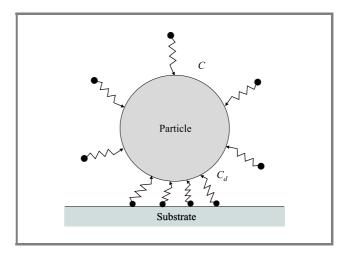

In fact, at very small particle/substrate distances, the major interactions caused by the charged surfaces are not due directly to the electrostatic forces but to the entropic contribution [9]. As shown in Fig. 4, the counter ion concentration is very high in between the particle and the substrate due to the overlap of the particle and substrate diffuse layers. This leads to the differential pressure between the top and bottom of the particle, expressed below:

$$F_e = (C_d - C) kT, \qquad (7)$$

where: k – the Boltzmann constant, T – absolute temperature, C – concentrations.

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

$<sup>^2\</sup>mathrm{Even}$  in the case of ultra pure water, there is a sufficient reservoir of  $\mathrm{H^+}$  and  $\mathrm{OH^-}$  of  $10^-7$  mole/L.

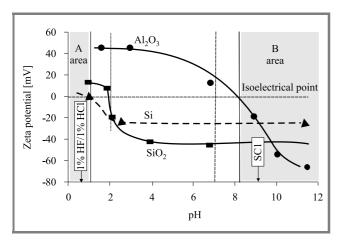

Figure 5 shows the evolution of the Zeta potential versus pH for Si and SiO<sub>2</sub> as substrate materials and one of the most electropositive particle materials – alumina.

$\it Fig. 5.$  Evolution of  $Al_2O_3$ , Si and  $SiO_2$  Zeta potentials versus pH.

In order to facilitate particle removal and to prevent any re-deposition it is to be hoped that charges gathered on all particle types and on the substrate are of the same sign leading to electrostatic repulsion. This condition is fulfilled in both A and B areas.

The forces originating from electrostatic charges can be calculated by solving the Poisson-Boltzmann equation [7]. They are favored by:

- high absolute values of surface potential (same electrical sign), the area B is generally better in this respect than the area A;

- high ionic force (densification of the diffuse layer increasing the entropic force);

- high temperature (kT factor in Eq. (7)).

#### 3. Particle removal mechanisms

Theoretical performances of conventional and prospective particle cleaning processes are discussed here.

#### 3.1. Cleaning by etching and electrostatic repulsion

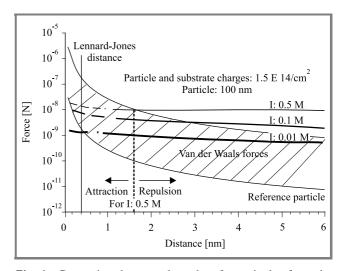

This cleaning mechanism consists in separating the particle from the substrate by consuming the substrate, the particles, or both, until the repulsive forces of electrostatic origin exceed the van der Waals forces. This means that the pH has to be adjusted in the area A or B. As shown in the example of Fig. 6, electrostatic forces decrease more slowly with the distance than van der Waals interactions. Therefore a liberation distance always exists regardless of the particle size and charge (theoretically 1.6 nm in the case of an ionic force of 0.5 M in Fig. 6).

Fig. 6. Comparison between the order of magnitude of van der Waals forces (hatched area) and forces of electrostatic origin at different ionic strengths as a function of the separation distance. Calculations of van der Waals forces for distances lower than 0.4 nm and calculations of electrostatic forces for distances lower than 2 nm are not valid.

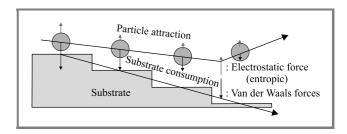

This theoretical etching thickness is increased in practice by the dynamic behavior of the removal process. Indeed, at the beginning of the separation, a competition occurs between the etching speed and the re-attraction speed of the particle due to van der Waals interactions (see Fig. 7).

Fig. 7. Illustration of the dynamic behavior of the particle removal process by etching and electrostatic repulsion.

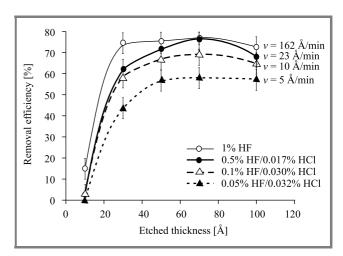

*Fig.* 8. Cleaning of 3000 SiO<sub>2</sub> particles deposited on a 200 mm SiO<sub>2</sub> substrate in HF solutions exhibiting different etching speeds (ionic strength and pH constant: 0.024 M and 1.4, respectively).

This phenomenon is verified in Fig. 8. When the etching speed is low, a higher material consumption is necessary to reach the nominal removal efficiency that is also lower. Particle removal processes, such as SC1 [2], IMEC clean [10], DDC [11, 12], etc., therefore have to present very fast etching kinetics. This requirement is compatible with the fast processes necessary for the new single wafer cleaning tools. Particle removal by etching and electrostatic repulsion does not seem to present any limitation in terms of particle size since the necessary consumption of the material is acceptable. In practice, this amount can be limited by increasing the etching speed, the ionic force of the solution and absolute values of Zeta potentials.

#### 3.2. Cleaning by drag forces

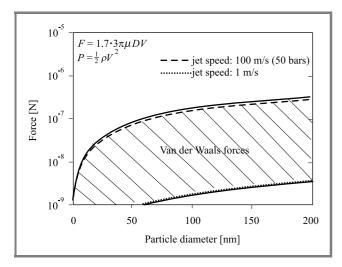

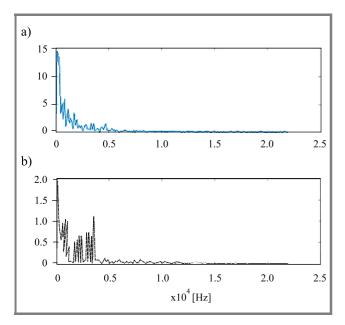

As shown in Fig. 9, drag forces induced by a continuous liquid jet are able to sweep along even very small particles. Nevertheless, very high pressures (50 bars) have to be used to have a chance of removing all particle types with a micro spray. In this calculation, we assume as the initial approximation that the thickness of the laminar boundary layer is zero just under the jet impact and that the order of magnitude of the drag force is approximated by (2). The jet therefore has to scan the whole wafer surface.

Fig. 9. Van der Waals and drag forces.

This cleaning method does not seem to be suitable for patterned wafers where particles are not accessible to the jet.

#### 3.3. Cleaning by shock waves

The instantaneous overpressure induced by a shock wave (water hammer) on the cross section area of a particle

generates a force likely to overcome the attractive van der Waals forces according to:

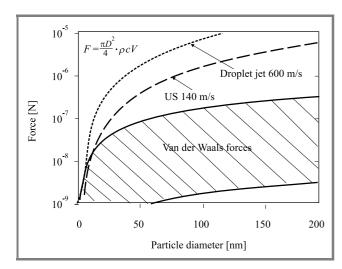

$$F_{shock} = \frac{\pi D^2}{4} \rho \, c \, V \,, \tag{8}$$

where: D – particle diameter,  $\rho$  – mass density of the media, c – wave velocity in the media (c = 1500 m/s in water), V – speed of the media versus the particle.

**Droplet jet.** The particle removal process using a jet of droplets called "Soft Spray" has recently been proposed. It consists in spraying a mixture of liquid and gas onto

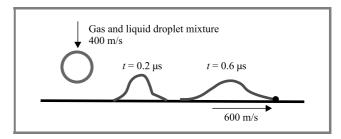

*Fig. 10.* Evolution of high velocity liquid droplet crashing at a perpendicular surface. Calculations taken from [13].

the wafer leading to a very high velocity heterogeneous jet. The generated droplet is projected onto the substrate with speeds in the range of 400 m/s. As represented in Fig. 10 calculations show that, when crashing, the droplet front even accelerates and strikes the particle at a speed of about 600 m/s [13]. Unlike a continuous jet, the exerted force is generated here by the shock wave from the droplet front applied to the particle surface.

**Resonant acoustic cavitation.** Cavitation in a liquid is due to the implosion of  $\mu$ -bubbles after the loss of the equilibrium pressure conditions between the inside and outside the bubble:

$$P_{in} - P_{out} = \frac{4 \, \gamma_{lg}}{D} \,, \tag{9}$$

The density of the energy liberated during bubble collapse is considerable as temperatures of 3000 K and pressures of 1000 atm are reached very locally. The bigger the bubble the higher the potential liberated energy. When a bubble collapses close to the surface, it can induce a microjet of liquid toward the surface that can reach a very high velocity of many hundreds of meters per second. This jet produces a very intense local shock wave. This phenomenon has been observed with a high-speed camera on bubbles in the mm range [14] and by nanosecond electrochemistry [15] with bubbles generated in an ultrasonic bath at 20 kHz. Acoustic cavitation has been observed in the megasonic range - up to 850 kHz - by sonoluminescence [16]. Nevertheless, it is not possible to conclude that the shock waves produced with megasonic frequencies that generate smaller bubbles are also induced by the same jet phenomenon.

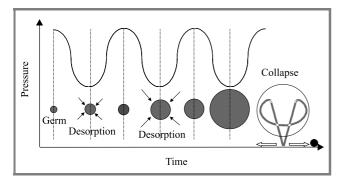

As shown in Fig. 11, the periodic pressure wave variations generated in a sonic bath tend alternatively to increase and

decrease the bubble diameter to satisfy (9). Bubbles are initially present as germs in the media. When a bubble grows, its exchange surface increases, making the desorp-

*Fig. 11.* Evolution of bubble sizes in an ultrasonic excitation until collapse (experimentally observed at the resonant size of the bubbles).

tion of the dissolved gas present in the supersaturated liquid easier. In this way, during the successive pressure cycles, the bubbles grow until they reach the resonant size that depends on the acoustic wave frequency.

In water, neglecting the effects due to surface tensions and considering the transformations as adiabatic, the resonant frequency  $f_0$  of bubbles is proportional to their radius R with a good approximation:

$$R_{[m]}f_{0[Hz]} \approx 3.26$$

. (10)

Thus  $R = 75 \mu m$  at 40 kHz and 3  $\mu m$  at 1 MHz.

At this frequency, the oscillation speed of the bubbles is maximum leading to the well known resonant cavitation phenomena observed in ultrasonic baths [17].

The megasonic efficiency strongly depends on the concentration and nature of the dissolved gas. High quantities of poorly soluble gas seem to be favorable for particle removal [18]. Acoustic wave transmission in the media

Fig. 12. Van der Waals and shock wave forces due to droplet jets and ultrasonic waves.

is limited by the presence of big bubbles. Acoustic waves generate different streamings that prevent reattachment by carrying the removed particles far from the surface [19]. Extensive efforts still have to be made to understand the actual removal mechanisms occurring in megasonic baths.

Cavitation is able to overcome van der Waals forces and, unfortunately, even to deteriorate the quality of the material. Using higher frequencies leads to smaller bubbles and consequently lower energies, which partly prevents material and pattern degradation but theoretically also decreases the removal forces for cleaning particles (limitation for the biggest size). Using a lower acoustic power leads to the same effect.

As shown in Fig. 12, the shock waves are theoretically able to remove all types and sizes of particles.

#### 3.4. Cleaning using capillary forces

Capillary forces can potentially remove particles when they are located at the liquid/gas interface. This configuration is achieved, for example, during fast evaporation of a liquid phase or when wafers cross the liquid/gas interface of a bath.

**Fast evaporation**. This consists first in depositing a liquid medium at the wafer surface and then evaporating this liquid phase very quickly by decreasing the pressure (Fig. 13). The last fragments of the liquid can pull the particles off by the capillary force (or by simple mechanical drive). Different fluids have been envisaged, such as H<sub>2</sub>O, CO<sub>2</sub>, NH<sub>3</sub>, ...

Fig. 13. Illustration of the cleaning principle by fast evaporation.

**Bath interface**. A.F.M. Leenaars [20] studied the capillary forces acting on a particle attached to a vertical substrate and located at the meniscus level of the air/liquid interface of a bath. In the particular case depicted in Fig. 14 (the liquid wets the substrate and not the particle), the maximum force is given by (11):

$$F_{\gamma}^{\text{max}} = 2\pi R \gamma_{lg} \sin^2\left(\frac{\theta}{2}\right) \cos\alpha. \tag{11}$$

As seen in Fig. 15, theoretically, the capillary forces are not able to remove all types of particles, even in the favorable case of particles perfectly hydrophilic in water (a case of high surface tension).

Fig. 14. Forces exerted on a particle attached to a substrate located at a gas/liquid interface.

*Fig. 15.* Evolution of the van der Waals and maximum capillary forces ( $\cos \alpha = 1$ ,  $\gamma_{lg} = 0.072$  N/m).

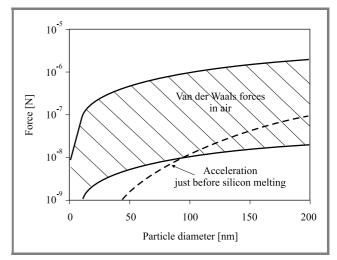

#### 3.5. Cleaning using high acceleration

A very high acceleration due to the thermal expansion of the substrate and/or the particles heated up with a laser beam is likely to remove particles [21]. In this case, the force exerted on a particle of mass m is, in the first approach, given simply by:

$$F = m\gamma. (12)$$

In practice, the acceleration is limited by the acceptable laser fluence leading to the melting of silicon. This threshold corresponds experimentally to the removal of the first alumina particles of about 100 nm (optimistic scenario). The corresponding acceleration calculated using Eq. (12) is in the 10<sup>6</sup> g range and thus higher than the one measured experimentally by Dobler *et al.* [22]. Anyway, as shown in Fig. 16, this method is not suitable for

removing fine particles. To improve the removal capability of laser cleaning, a thin layer of liquid is first condensed from steam onto the substrate. In this case, the cleaning

*Fig. 16.* Evolution of the van der Waals forces and the force generated by an acceleration able to remove the first 100 nm alumina particles, in air.

mechanism proposed by [21] would be close to the phenomenon of the cavitation process depicted above and consequently to its performance.

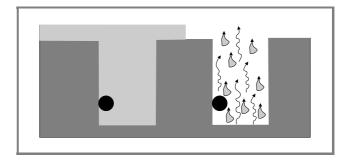

#### 3.6. Cleaning by kinetic energy

In 1988, researchers at IBM Watson Research Center began to study cryogenic particle removal. This process uses the kinetic energy of a distribution of solid aerosol particles obtained for example by expansion cooling of gas such as Ar, N2, etc., [23]. This aerosol is then eliminated by sublimation. The particles just liberated are evacuated far from the substrate by thermophoresis or by a gaseous flow. If we consider that only one aerosol particle of mass m and velocity V reaches the particle at any one time, the removal condition is given by:

$$\int_{h_0}^{\infty} \frac{AR}{6h^2} dh = \frac{AR}{12h_0} = \frac{1}{2} mV^2.$$

(13)

Collective effects may however occur.

In order to be able to remove particles located in lines and vias, the aerosol particles have to be smaller than the pattern dimensions.

#### 4. Conclusion

In this work a range of van der Waals interactions covering 2 orders of magnitude is considered to take into account the majority of the variety of shapes and materials of the actual particles. This range has been determined by considering

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

the possible variations of the Hamaker constant and the difference between the ideal rigid sphere and real particles presenting finite contact areas, flattening effects, etc.

The different particle removal processes can be classified according to the physical effects used, such as electrostatic, drag and capillary forces, shock waves, acceleration, or kinetic energy. By comparing the attractive van der Waals forces and those generated by these effects it is then possible to predict the intrinsic capabilities and limitations of the different cleaning processes, particularly for the fine particles that have to be considered for the next IC generations. Three kinds of particle removal processes have been identified, namely universal processes able to remove all particle sizes and types even from patterned wafers, processes that present the same theoretical ability but are actually limited by the accessibility of the particles, and finally cleanings that are not able to remove all particle sizes.

- Particle removal by etching and electrostatic repulsion is the process used the most often through the SC1 cleaning step. This method does not seem to present any limitation in terms of particle size since the necessary material consumption is acceptable. In practice, this amount can be limited by increasing the etching speed, the ionic force of the solution and absolute values of Zeta potentials. It is also possible to remove all particle types by shock waves generated for example by megasonics in aqueous media. Nevertheless this method is limited by the erosion of the materials and by the mechanical resistance of the microstructures.

- High-speed aqueous jets, droplet jets, and aerosol sprays are theoretically able to remove all particle types accessible to the jet. Limitations arise from the mechanical resistance of the patterns and for particles hidden in the microstructures.

- Methods using capillary forces and high accelerations are not able to remove all particle types.

#### References

- [1] International Technology Roadmap for Semiconductors, 2001, http://public.itrs.net/Files/2001ITRS/Home.htm

- [2] W. Kern and D. Puotinen, "Cleaning solutions based on hydrogen peroxide for use in silicon semiconductor industry", RCA rev. 31, p. 187, 1970.

- [3] F. Tardif, Nettoyages par voie humide en micro-électronique dans l'ouvrage "Procédés de fabrication en micro-électronique". Hermes Science Publ., 2003.

- [4] R. Comolet, Mécanique expérimentale des fluides. Tome II, 3rd ed. Paris: Masson, 1982.

- [5] M. O'Neill, "A sphere in contact with a plane wall in a slow linear shear flow", Chem. Eng. Sci., vol. 23, p. 1293, 1968.

- [6] G. Ziskind, M. Fishman, and C. Gutfinger, "Resuspension of particulates from surfaces to turbulent flows. Review and analysis", J. Aerosol Sci., vol. 26, pp. 613–644, 1995.

- [7] J. Israelachvili, *Intermolecular & Surface Forces*. 2nd ed. Academic Press, 1997.

- [8] P. C. Hiementz, Principle of Colloid and Surface Chemistry. 2nd ed. New York: Dekker Press, 1986.

- [9] F. Tardif, I. Constant, R. J.-M. Pellenq, and A. Delville, "A new approach for particle removal based on a Monte Carlo simulation of electrostatic interactions", in 7th Int. Symp. Part. Surf., New York, USA, 2000.

- [10] M. Meuris, P.-W. Mertens, A. Opdebeeck, H.-F. Schmidt, M. Depas, G. Vereecke, M.-M. Heyns, and A. Philipossian, "The IMEC clean: a new concept for particle and metal removal on Si surfaces", *Solid-State-Technol.*, vol. 38, no. 7, pp. 109-110, 112, 114, 1995.

- [11] F. Tardif, T. Lardin, C. Paillet, J. P. Joly, A. Fleury, P. Patruno, D. Levy, and K. Barla, "Optimization of HF and oxidant wet cleanings before 7 nm gate oxide: introduction to "DDC": diluted dynamic clean", in ECS, Chicago, USA, 1995.

- [12] F. Tardif, T. Lardin, B. Sandrier, P. Boelen, R. Matthews, I. Kashkoush, and R. Novak, "Performances of "DDC": diluted dynamic clean before 4.5 nm gate oxide", in ECS, Paris, France, 1997.

- [13] N. Hirano, K. Takayama, J. Falcovitz, T. Katoaka, K. Shimada, and E. Ando, "Microscopic analysis of particle removal by gas/liquid mixture high-speed flow", in *UCPSS'98*, Oostende, Belgium, 1998.

- [14] J. C. Isselin, A. P. Alloncle, and M. Autric, "On laser induced bubble near a solid boundary: contribution to the understanding of erosion phenomena", J. Appl. Phys., vol. 84, no. 10, pp. 5766–5771, 1998.

- [15] E. Maisonhaute, P. C. White, and R. G. Campton, "Surface acoustic cavitation understood via nanosecond electrochemistry", *J. Phys. Chem. B*, vol. 105, pp. 12087–12091, 2001.

- [16] D. Zhang, "Fundamental study of megasonic cleaning". Ph.D. thesis, University of Minnesota, 1993.

- [17] L. H. Thompson and L. K. Doraiswamy, "Sonochemistry: science and engineering", *Ind. Eng. Chem. Res.*, vol. 38, pp. 1215–1249, 1999.

- [18] P. Besson, O. Keller, and G. Ching, "Particle removal evaluation in DI water with megasonic activation", in *Techn. Conf., Semicon. Eur.*, Munchen, Germany, 2002.

- [19] A. Busnaina, J. Taylor, and I. Kashkoush, "Measurement of the adhesion and removal forces of sub micrometer particles on silicon substrates", J. Adhes. Sci. Technol., vol. 7, p. 441, 1993.

- [20] A. F. M. Leenaars, "Particles on surfaces I: detection, adhesion and removal", Ed. K. L. Mittal. New York: Plenum Press, 1988.

- [21] X. Wu, E. Sacher, and M. Meunier, "The modeling of excimer laser particle removal from hydrophilic silicon surfaces", *J. App. Phys.*, vol. 87, no. 8, pp. 3618–3627, 2000.

- [22] V. Dobler, R. Oltra, J. P. Boquillon, M. Mosbascher, J. Boneberg, and P. Leiderer, "Surface acceleration during dry laser cleaning of silicon", *Appl. Phys. Mat. Sci. & Proc. A*, vol. 69, pp. 335–337, 1999.

- [23] J. J. Wu, D. Syverson, T. Wagner, and J. Weygand, "Wafer cleaning with cryogenic argon aerosols", in *Semicon. Int.*, Boise, USA, 1996.

François Tardif is the Head of the Ultra Clean Process Laboratory in the Microelectronics Department at CEA-Leti, Grenoble, France. He graduated from the engineering school of l'Institut National des Sciences Appliquées in Toulouse and received the Ph.D. degree in materials sciences from the University of Marseille, Marseille,

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

France. He is a member of the Electrochemical Society, he has co-organized congresses in the fields of silicon cleaning and ultra trace contamination measurements and has authored more than 50 papers.

e-mail: TardifFr@chartreuse.cea.fr CEA Leti 17 rue des Martyrs F-38054 Grenoble cedex 9, France

Adrien Danel received the diploma in engineering in 1994 and the Ph.D. degree in physics and microelectronics from the National Polytechnical Intitute of Grenoble, France, in 1999. He is a research engineer at CEA Leti, working with silicon surface characterization by non-invasive methods and focusing on advanced

cleaning processes. e-mail: DanelAd@chartreuse.cea.fr CEA Leti 17 rue des Martyrs F-38054 Grenoble cedex 9, France

Olivier Raccurt received the B.Sc. degree in physics from the Université Claude Bernard, Lyon, France, in 2000, and the M.Sc. degree in materials science from the Institut National des Sciences Appliquées, Lyon, France, in 2001. He received the Ph.D. degree in physics and material science from the Université

Aix-Marseille, Marseille, France, in 2004. This work was conducted at CEA Leti, Grenoble, France, and was focused on the mechanisms of stiction of microsystems during releasing step, involving studies on etching processes and cleaning of silicon substrate for micro-electronics, using atomic force microscopy for topological characterisation. He is currently holding a postdoctoral position at CEA Leti, where he is working on electrowetting on dielectric to move small droplets of biological liquid within the framework of a lab-on-chip project. His current research interests include the behaviour of liquid on solid at microscale dimension and atomic force microscopy characterisation.

e-mail: RaccurtOl@chartreuse.cea.fr CEA Leti 17 rue des Martyrs F-38054 Grenoble cedex 9, France Invited paper

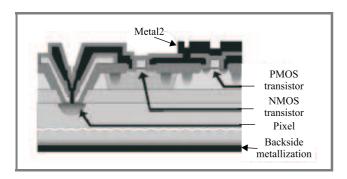

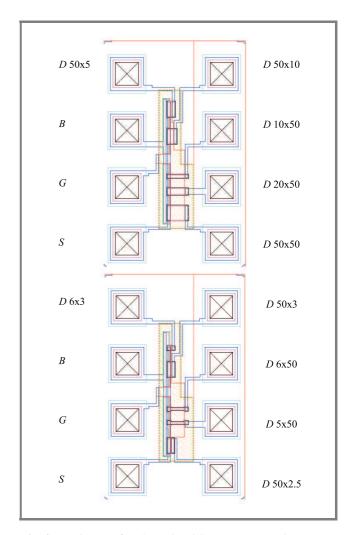

## Integrated gas chromatograph

Jan A. Dziuban, Jerzy Mróz, and Jan Koszur

Abstract—A portable gas chromatograph with integrated micromachined flushed injector and thermal mass detector (TCD) has been developed. The silicon/glass injector operates in a fixed volume ( $2\times7~\mu L$ ) or electronically operated mode. An integrated, pneumatically operated, fast cross-valve is applied in the injector. The TCD detector consists of two Pt microheaters and thermoresistors packaged in a silicon/glass micromachined chip. The temperature of two capillary molecular sieve separation columns is controlled by a thick-film heater fabricated on polyimide foil. The chromatograph is equipped with two 16-bits microprocessors communicating with the external portable PC. The instrument may operate in the on-line continuous analysis mode.

Keywords—portable gas chromatograph, integrated injectors, silicon micromechanics.

#### 1. Introduction

In this paper the results of a long-lasting research program on portable gas chromatograph are presented. The program was carried out under the auspices of the State Committee for Scientific Research. The main goal of the research was to obtain a miniature gas chromatograph (GC) with a flushed gas injector and fast, nano-dead-volume TCD. The device is equipped with appropriate software and analog/digital circuits and is capable of ensuring continuous detection of combustible atmosphere in deep coal mining industry and/or continuous monitoring of the environment (long-term air quality, drifts, emission of polluters, etc.).

#### 2. Experiment

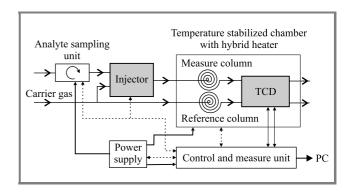

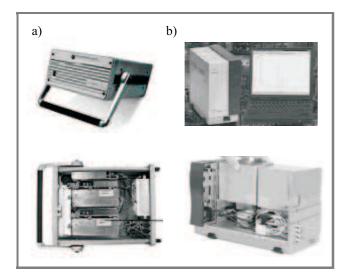

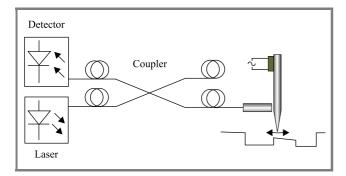

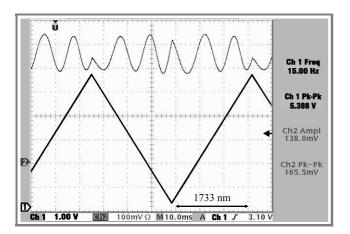

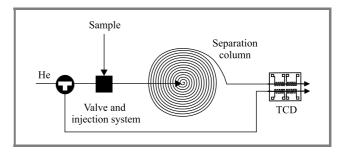

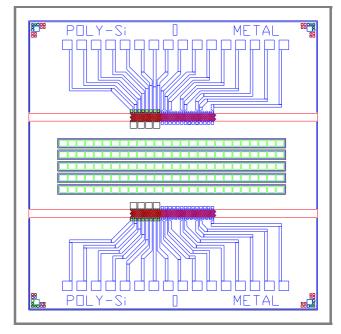

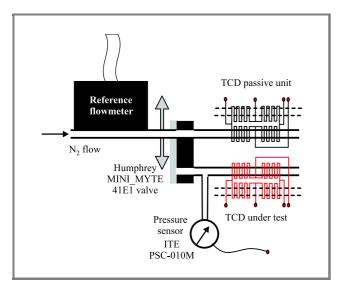

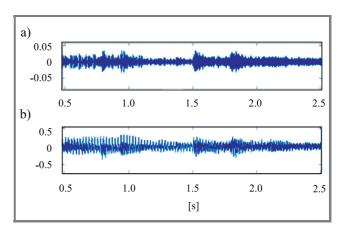

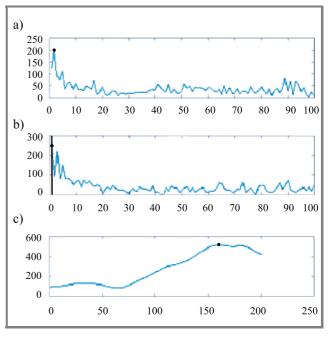

The portable gas chromatograph consists of two micromachined parts: a fixed or electronically adjusted gas injector and thermal-mass-detectors. Restek (USA) ID 0.32 mm Rt-Msieve 5A capillary columns, each 10 m long, are positioned in a thermally isolated chamber. A thick-film heater fabricated on elastic polyimid foil surrounds the columns and ensures proper adjustment and stabilization of the temperature (50–120°C) (see Fig. 1).

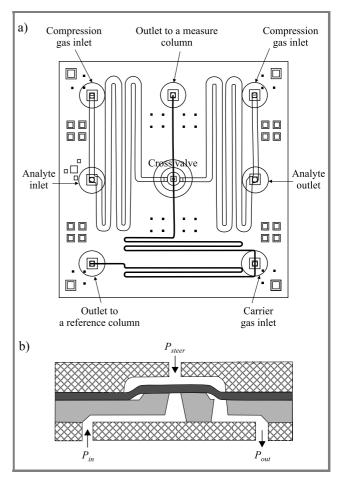

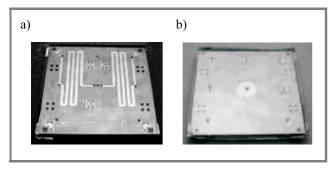

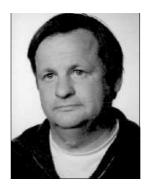

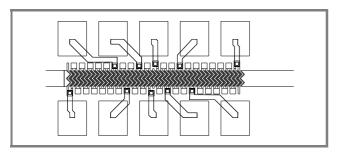

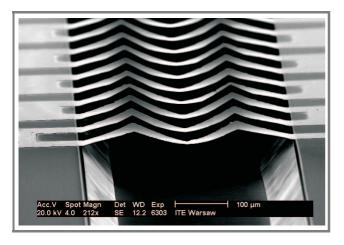

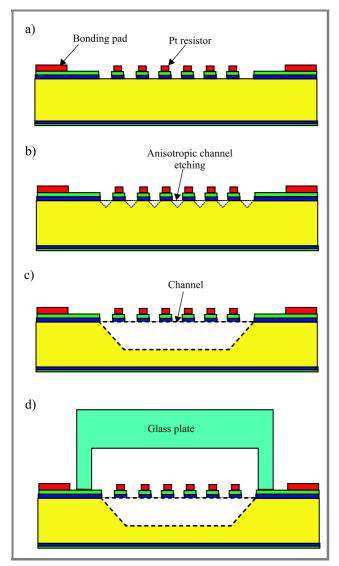

The injector consists of two Borofloat 33 glass substrates, silicon (100) deep-micromachined substrate polished on both sides, and polyimide foil coated with Teflon®. The gas circuit of the injector includes one integrated fast cross-valve (1 ms) operated pneumatically, two fixed-volume chambers (7  $\mu$ L each) and two narrow channels for active and reference gas column supplying (Fig. 2). The fabrication process of the injector includes new processes of 3D-structure substrate-by-substrate assembling: selective bonding of glass and silicon substrate using polyimide foil (Fig. 3).

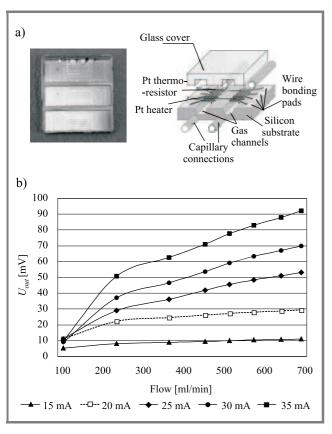

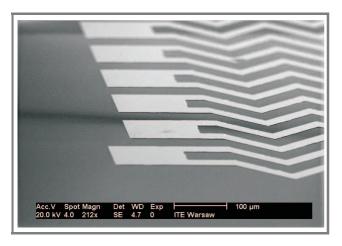

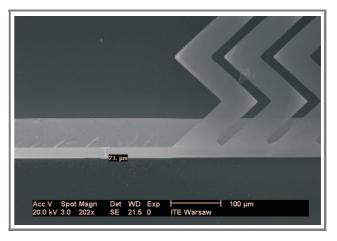

The TCD sensor applied in the GC has been designed and fabricated by the Institute of Electron Technology in Warsaw. In the device a thin-film Pt heater and a thermo-resistor

*Fig. 1.* Block diagram of the gas chromatograph with integrated micromachined components – gas injector and TCD sensor (grey areas).

*Fig. 2.* The injector: (a) layout of the device; (b) cross-section of a microvalve; for  $P_{steer} < P_{in}$  the microvalve is closed.

*Fig. 3.* The injector: (a) front-side: gas channels, fixed volume chambers and microvalve (in the middle) may be seen; (b) back-side view: analyte, carrier gas and control pressure inlets.

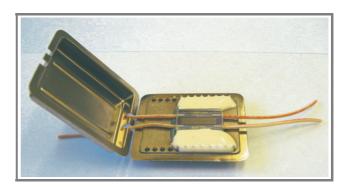

have been formed on a perforated membrane made of a double-layer  $SiO_2/Si_3N_4$  system fabricated using LPCVD. The membrane extends over a gas channel formed by means of deep wet etchnig of a (100) silicon wafer. This structure is covered with a glue-bonded, 1 mm thick glass plate. The device chip is assembled with the capillaries and packaged in a metallic case, then wire-bonded connections are made (Fig. 4).

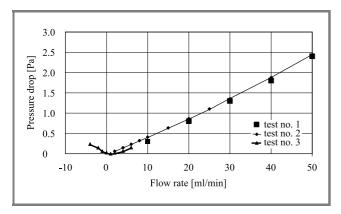

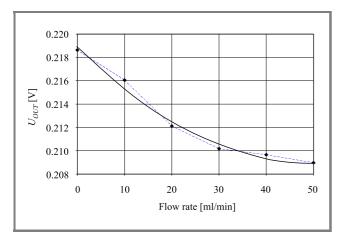

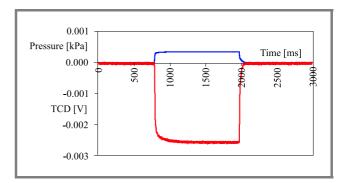

*Fig. 4.* TCD detector: (a) diagram (right) and view of the fabricated device (left); (b) most important characteristics –  $U_{out}$  versus  $N_2$  flow for different levels of supply current.

In the solution reported here two independent sensors have been formed in a single chip and connected in the full Wheatstone bridge configuration in the self-calibrating mode.

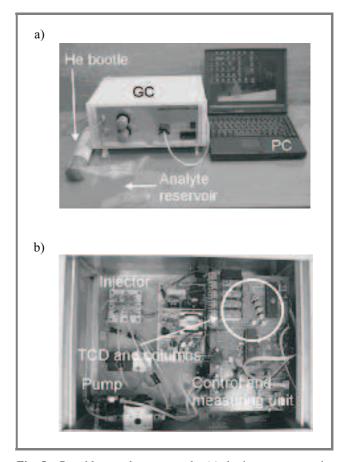

Fig. 5. Portable gas chromatograph: (a) the instrument, carrier gas bottle, and PC; (b) inside view.

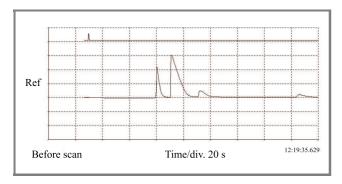

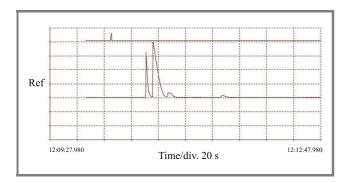

Fig. 6. Results of analysis: (a) electrical output signal and virtual control board of the GC; (b) processed chromatogram of a gas mixture and data table.

## Table 1 Technical parameters of the GC reported here

#### Dimensions/weight:

15 cm  $\times$  45 cm  $\times$  30 cm/ $\sim$  3.5 kg

#### **Environmental conditions:**

Indoor, automatic sampling from atmosphere (build in pump) or external source of analyte

#### Supply:

230 V<sub>(AC)</sub>, 50-60 Hz, 200 VA

#### Carrier gas:

Helium carrier gas, external source, min. pressure 220 kPa

#### Analysis time:

Depends on gas mixture and applied column, 400-700 s

#### Injector

Silicon/glass micromachined with polyimide membrane, the volume of injected analyte determinated by cross-valve open time or total volume of the dosage loop (14  $\mu$ L  $\pm 1\%$ ), possible backflush and independent temperature stabilization

#### **Detector:**

Silicon/glass micromachined two-way thermo conductive detector (TCD) with four Pt micro spirals set up in auto compensating Whetsfone's bridge circuit, death volume in nL range

#### Chromatographic column:

Depends on application (RT-Msieve 5 A, 10 m long, temperature  $50-150^{\circ}$ C)

#### Control unit/software:

External PC laptop-type with RS 232 or USB port, specialized software under Windows98/NT/2000/XP platform, all parameters of analysis electronically adjusted

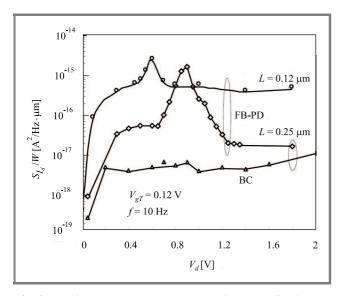

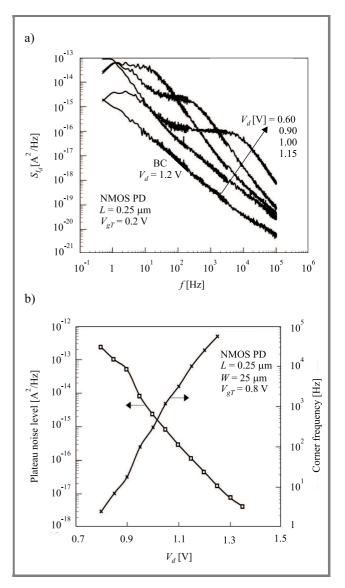

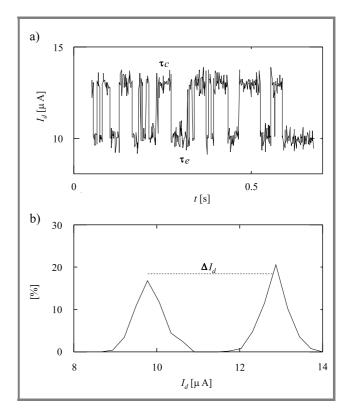

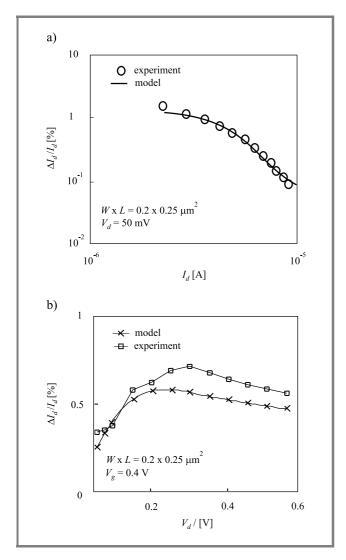

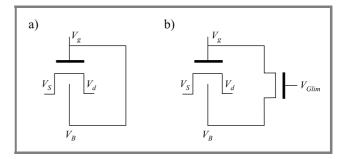

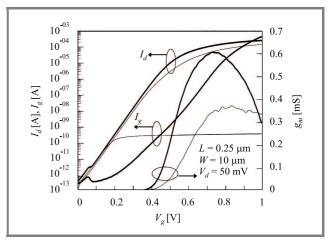

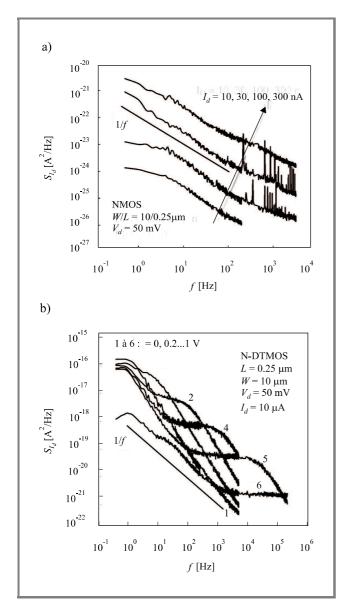

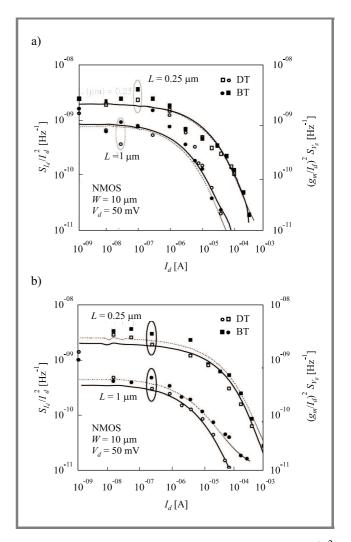

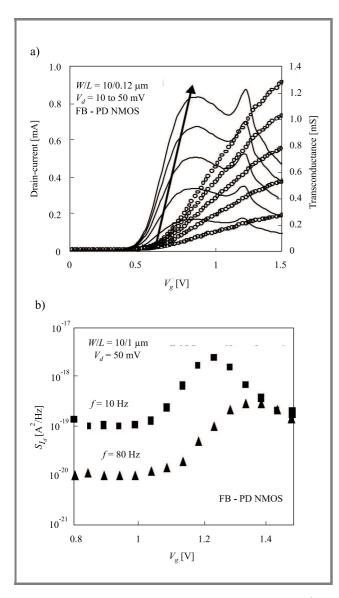

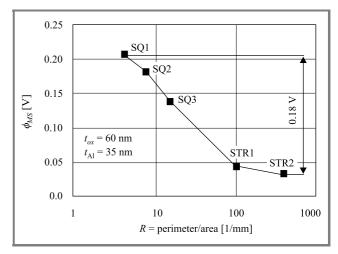

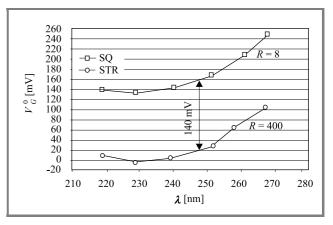

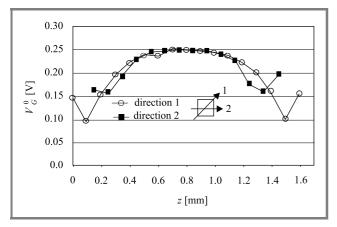

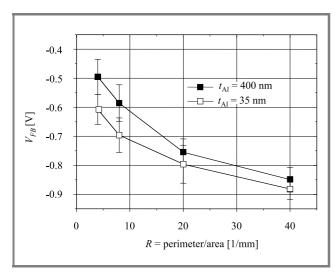

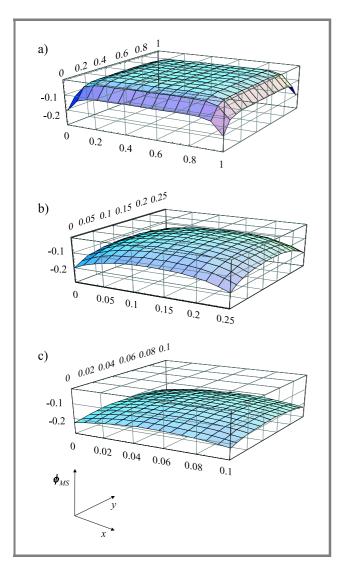

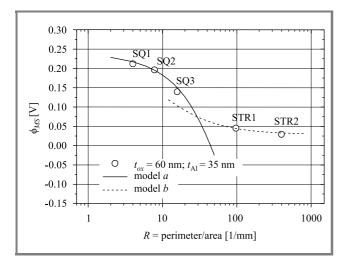

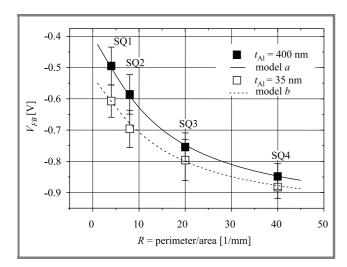

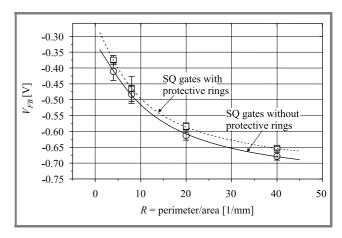

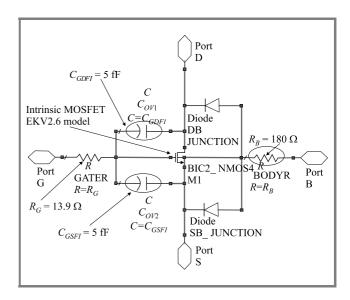

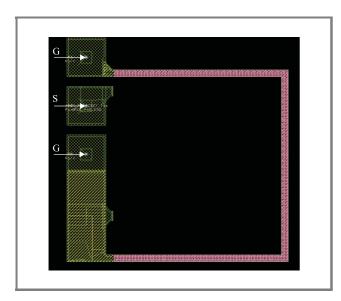

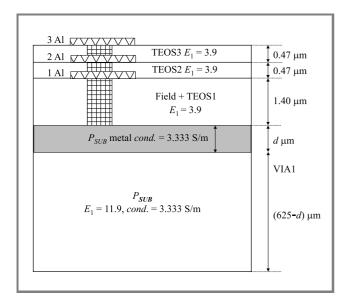

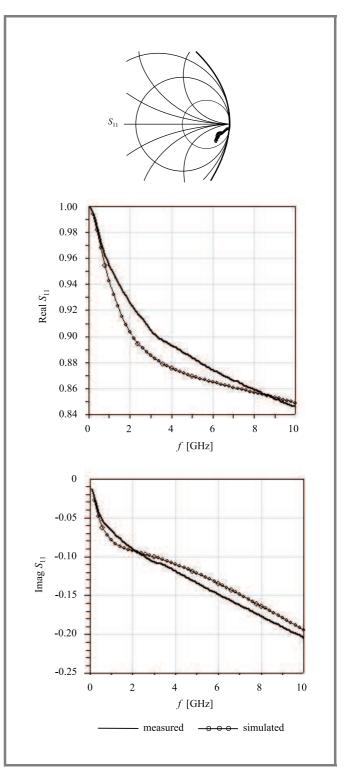

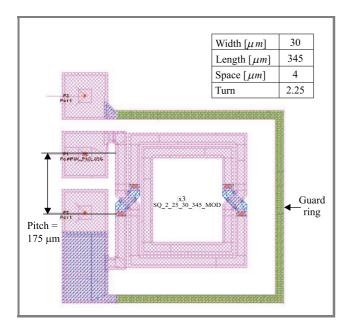

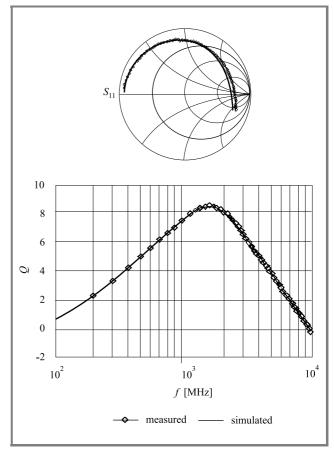

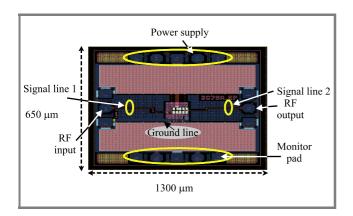

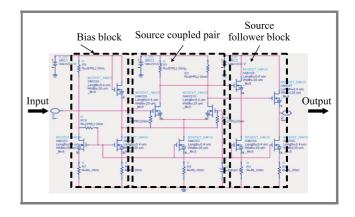

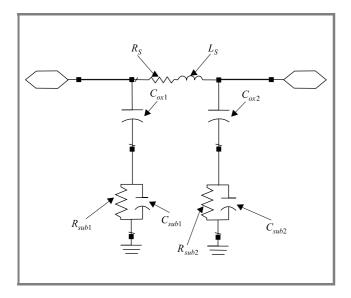

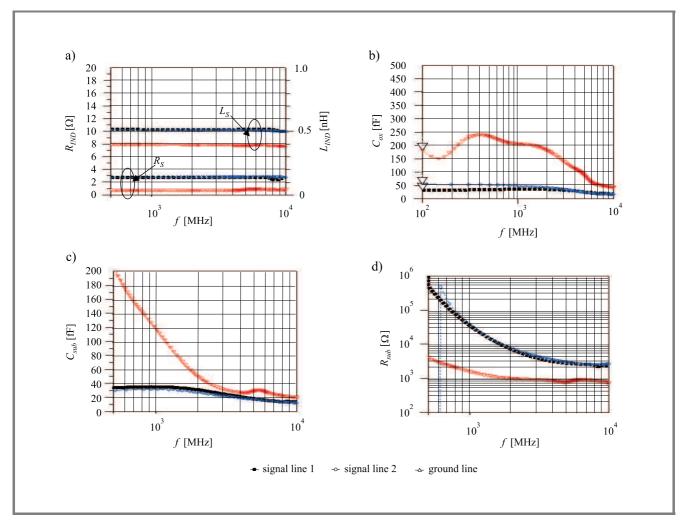

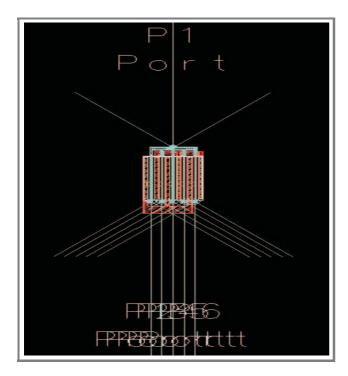

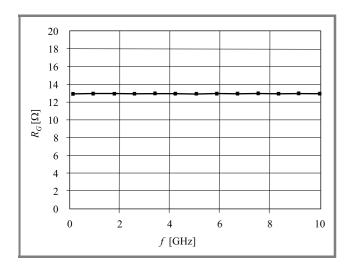

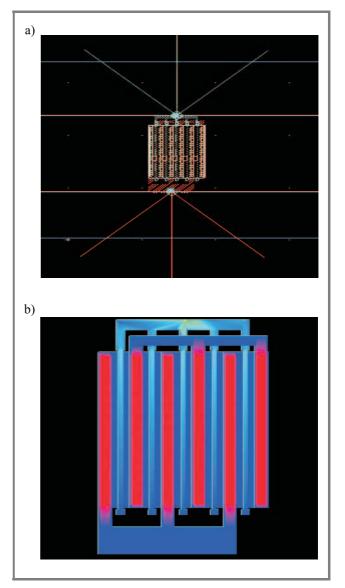

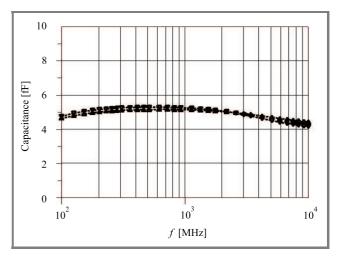

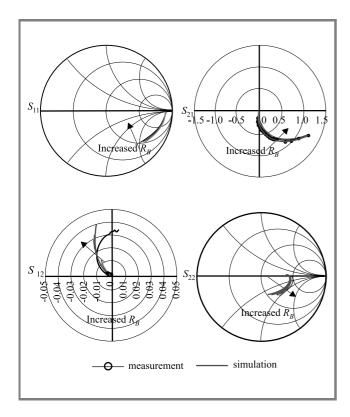

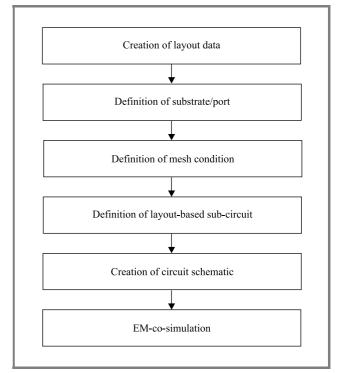

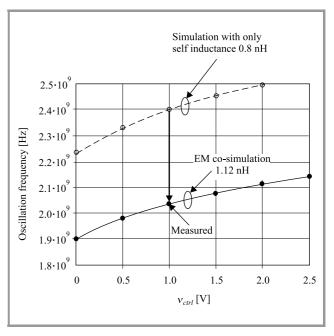

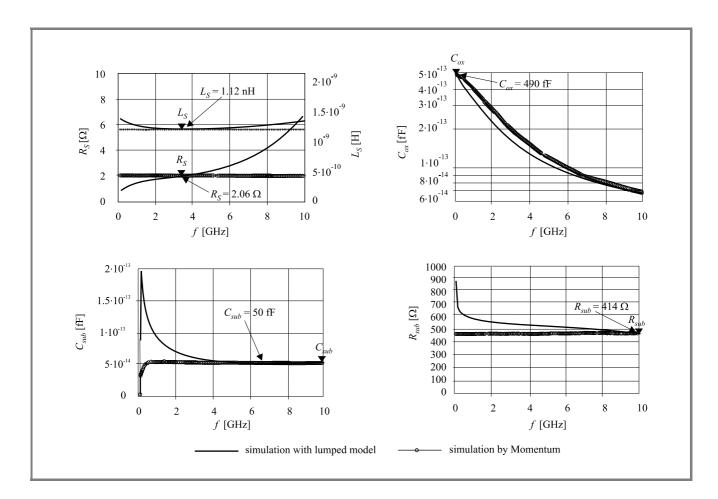

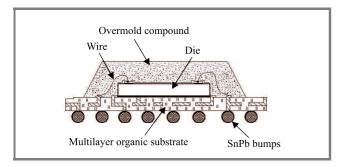

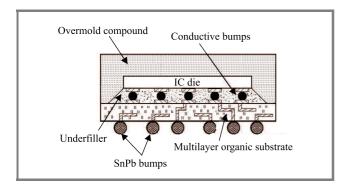

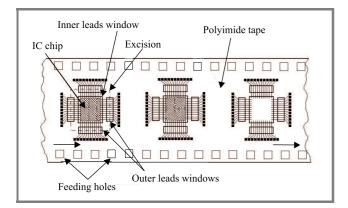

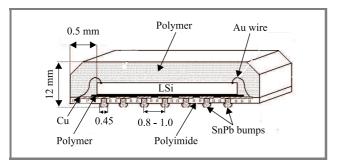

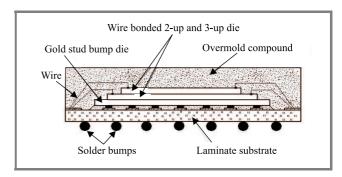

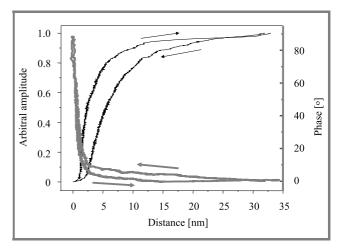

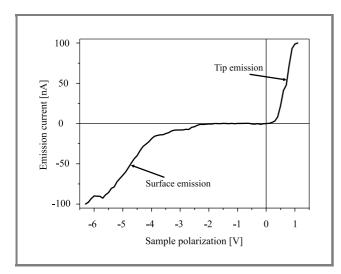

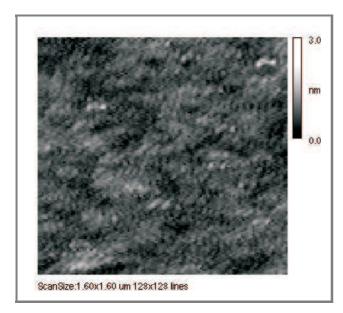

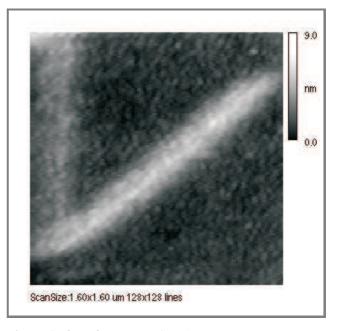

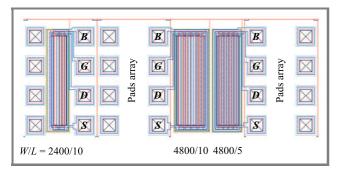

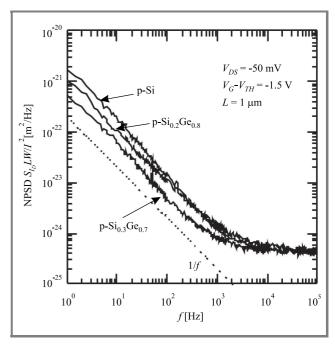

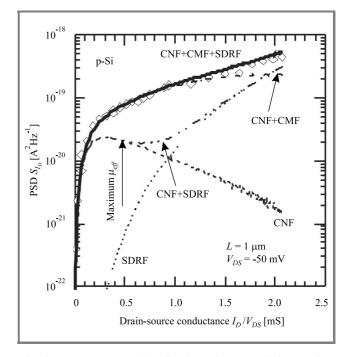

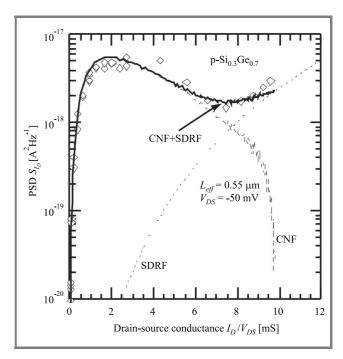

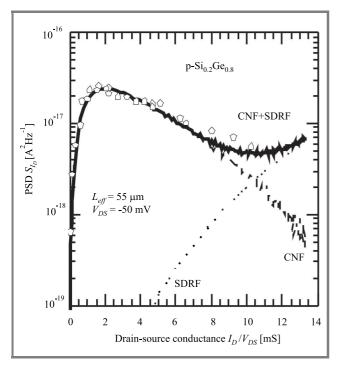

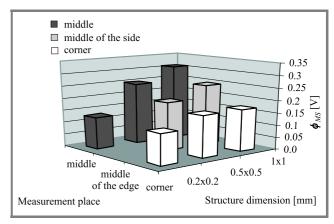

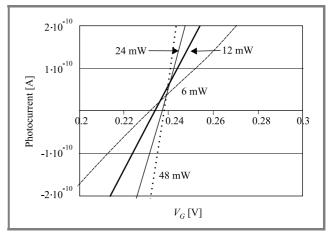

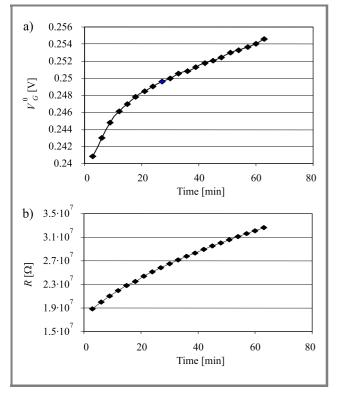

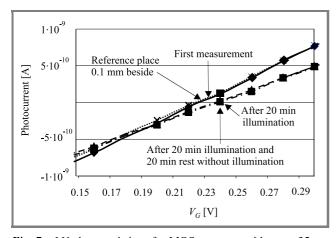

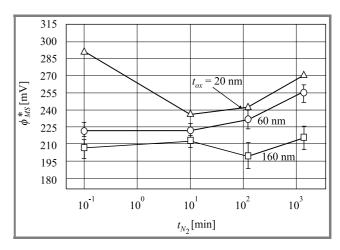

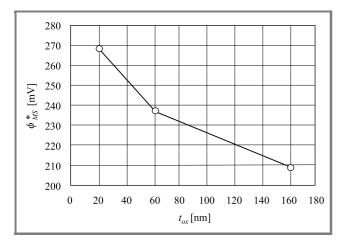

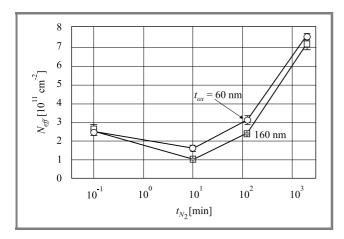

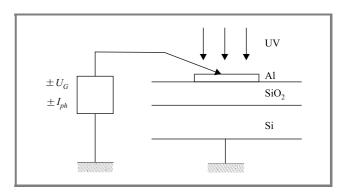

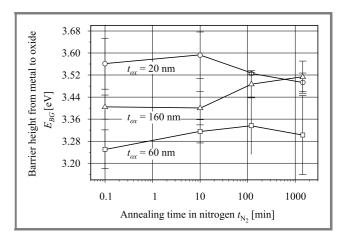

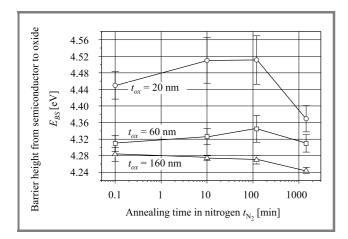

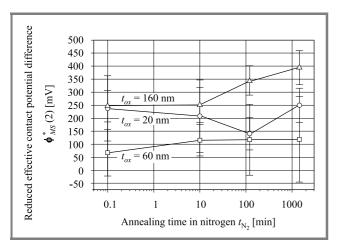

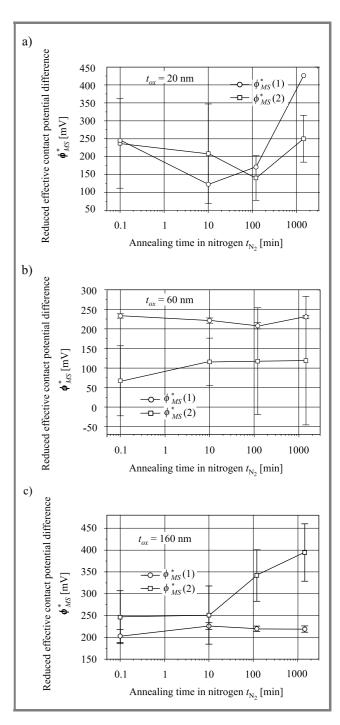

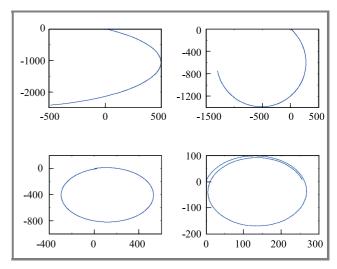

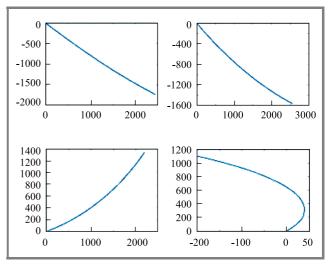

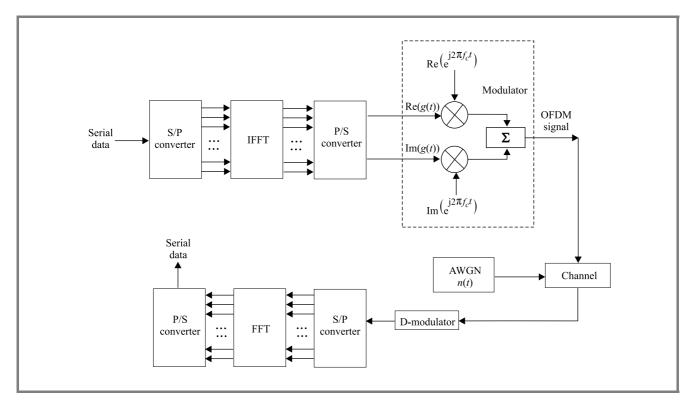

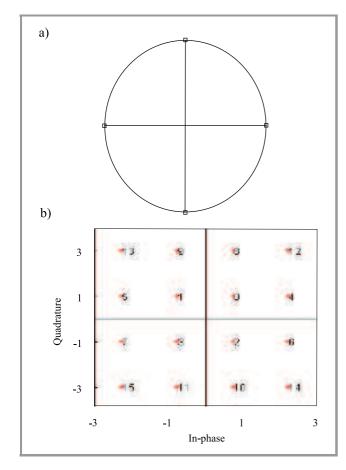

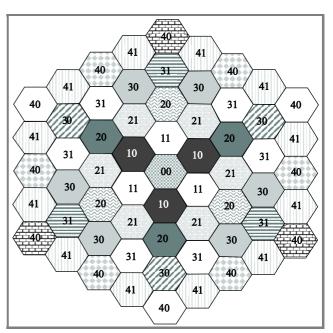

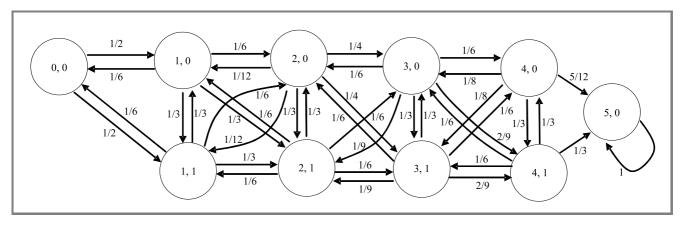

*Fig.* 7. The competing portable GCs: (a) Agilent 3000 Micro-GC; (b) Varian CP-4900 Micro-GC.