Invited paper

# **Challenges in scaling of CMOS devices towards 65 nm node**

Małgorzata Jurczak, Anabela Veloso, Rita Rooyackers, Emmanuel Augendre, Sofie Mertens, Aude Rotschild, Marc Scaekers, Richard Lindsay, Anne Lauwers, Kirklen Henson, Simone Severi, Ivan Pollentier, and An de Keersgieter

Abstract—The current trend in scaling transistor gate length below 60 nm is posing great challenges both related to process technology and circuit/system design. From the process technology point of view it is becoming increasingly difficult to continue scaling in traditional way due to fundamental limitations like resolution, quantum effects or random fluctuations. In turn, this has an important impact on electrical device specifications especially leakage current and the circuit power dissipation.

Keywords—CMOS devices, gate dielectrics, shallow junctions, silicide, gate stack, lithography, gate patterning, silicon recess, device integration.

#### 1. Introduction

The traditional scaling approach, which has been the base of the semiconductor industry for the last 30 years is beginning to show the fundamental limits of the materials building the modules of a planar CMOS transistor. Significant efforts are being devoted to the introduction of new materials that will replace the existing ones to further extend the device scaling process.

However, even though the new materials and device architectures are being investigated, the gate length scaling below 60 nm has a significant impact on the electrical properties of the devices. The continuous thinning of the gate dielectric layers, the increasing channel doping and the aggressive, abrupt junctions, required to control the short channel effects, start to significantly affect circuit power dissipation.

Nitrided oxides, gate predoping, offset spacers, spike anneal, tilted pocket implants, ultra low energy implants are a few examples of the process steps that were introduced in the 0.13  $\mu$ m technology generation to enable device gate length scaling. These previous "improvements" will be able to prolong scaling down to 65 nm node. New solutions to device architecture, device substrate, gate stack will have to be introduced to maintain 12% increase in device performance forecasted by ITRS roadmap [1].

This paper gives an overview of the main challenges being faced in the front-end of line (FEOL) technology development for 65 nm node. This includes the gate stack, gate patterning, junction and silicide process.

#### 2. Gate stack

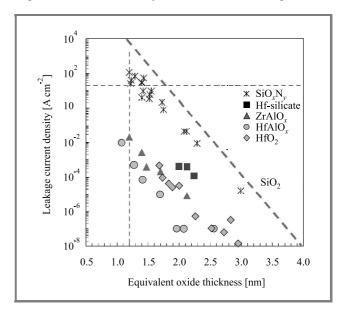

Aggressive scaling of CMOS devices puts severe constrains on the gate dielectric. In order to meet requirements for drive current and off-state leakage set up by ITRS roadmap it is essential to simultaneously scale further gate oxide thickness and limit the gate leakage current. In addition, mobility degradation has to be minimized and gate oxide reliability still has to meet the 10-year lifetime requirements. Despite low gate leakage current as compared to nitrided oxides (Fig. 1), high-*k* dielectrics are still not ready for device integration due to reliability problems, high mobility degradation and instability of the threshold voltage.

Fig. 1. Comparison of different gate dielectrics with respect to gate leakage and EOT.

Therefore, there is strong motivation to extend the use of oxynitrides to its ultimate limits. Oxynitrides fabricated with a new plasma nitridation techniques such as decoupled plasma nitridation (DPN) [2] or slot plane antenna (SPA) seem to be the best candidates for 65 nm high performance and general purpose CMOS devices (Fig. 1) at least until high-k materials reach their maturity for the gate dielectric applications. Using plasma nitridation it is possible to introduce more nitrogen than with furnace nitridation techniques into thin oxide layer and thus increase the dielectric constant k and scale equivalent oxide thickness without reducing significantly physical oxide thickness [3].

Continued thinning of gate dielectrics and an increase of the interface-state density created by plasma nitridation bring many concerns related to reliability issues. Thorough characterization shows, however, that a careful optimization of the gate dielectric process enables maintaining the maximal operation voltage, at which the device can be operational for 10 years, above the supply voltage [4]. This is possible since oxide reliability is dependent rather on physical oxide thickness than on EOT.

The gate activation, which has direct impact on the drive current, is more and more affected by the reduced thermal budged required in order to control short channel effects. Additional gate implantation called gate predoping is mandatory to maintain low gate depletion. Metal gate seems to be a solution to this problem, however, due to the unsuitability of the work function and highly complex integrity it will not be ready for the 65 nm node.

# 3. Gate patterning

In order to cope with progressive scaling of CMOS devices new lithography techniques are being investigated. The 157 nm lithography is considered as the leading candidate for semiconductor device manufacturing at the 65 nm technology node [5]. However, development of 157 nm lithography requires considerable effort and effective solutions to resist and reticle materials, lenses, CD metrology, etc. This list of challenges raises fears that the 157 nm lithography will not be ready for the 65 nm node. Therefore, other methods such as resist or hard mask trimming were developed to support lithography in the scaling progress.

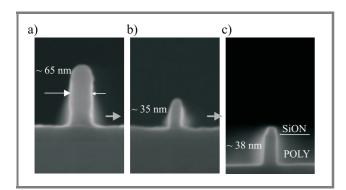

In the 65 nm node, where the gate length is in the range of 65–25 nm, depending on applications, the key process step developments are lithography, dry etch, and CD metrology. With respect to lithography, the emphasis is put on the development of thin resist processes (using 193 nm lithography) in combination with alternating phase shift mask (AltPSM) optical extensions. With this combination the lines down to 65 nm with good CD control can be printed (Fig. 2a). Further reduction of the gate length is obtained by subsequent resist or hard mask trim-

Fig. 2. Visualization of the trim and gate etch: (a) showing the X-section of features after litho; (b) etch trim; (c) gate etch and strip.

ming (Fig. 2b). Trimming techniques allow obtaining gate lengths down to a few nanometers.

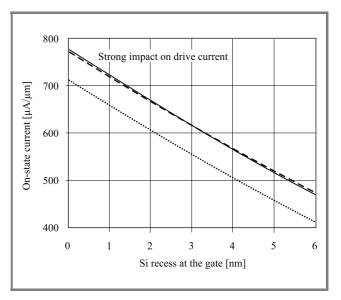

Fig. 3. Impact of Si recess created at the gate patterning on the drive current (simulation results).

An important issue when scaling devices and the gate oxide thickness is silicon recess in source and drain areas which occurs during overetch step in gate electrode patterning. Even small, a few nanometers consumption of Si in the substrate has considerable impact on device performance and leads to increase in the off-state leakage and series resistance (Fig. 3).

#### 4. Junction

Approaching the 65 nm node ITRS requirements for ultrashallow junctions (USJ) has become a great challenge, es-

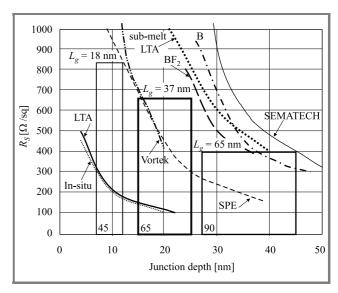

*Fig. 4.* Summary of p<sup>+</sup>/n junctions obtained with different techniques. The boxes indicate the requirements for different technology generations (literature results).

1/2005

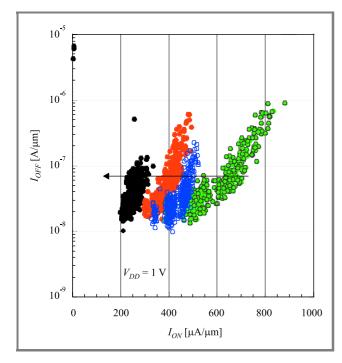

Fig. 5. Drive current versus off-state leakage for NMOS devices with different doses in extensions. The arrow indicates the reduction in the doping concentration in the junctions.

Fig. 6. Impact of offset spacers on control of short channel effects.

pecially for p<sup>+</sup> dopants. With boron, traditionally used for p<sup>+</sup>/n junction formation, implanted alone and annealed with conventional methods, the 90 nm node specifications can hardly be reached (Fig. 4). Simple lowering of implantation dose reduces the junction depth but on the other hand leads to high series resistance and degradation of the on-state current (Fig. 5). The literature data shows that only with very sharp spike anneal (high rump-up and rump down using, e.g., Levitor or Vortek tool) the improvement in the trade-

off between junction resistance and junction depth can be achieved [6]. Even better results can be obtained with a co-implantation with other elements and/or pre-amorphization implants in conjunction with spike anneal. The combination of Ge pre-amorphization, F co-implantations and fast rampup spike anneal appeared to be sufficient to fulfill the 65 nm node requirements [7]. For the next generation other alternative routes of forming the junctions such as solid phase epitaxial re-growth (SPER) [8] or laser anneal (LTA) are investigated.

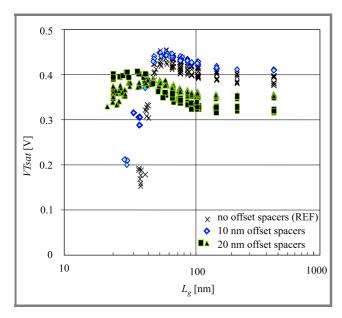

Introduction of offset spacers allows relaxing the requirements for the extensions without aggravating short channel effects (Fig. 6). This, however, puts very severe constrains on their width control since any small variations in the spacer width may result in huge variation in VT and offstate leakage.

## 5. Silicide

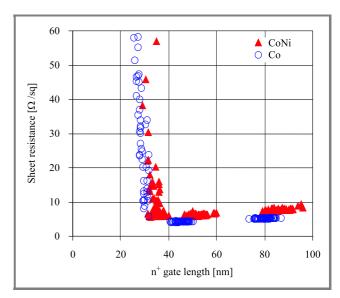

The scaling of the gate length (below 40 nm) goes in parallel with the reduction in the HDD junction depth. Shallower junctions, in turn, determine more constrained requirements for the silicides. Conventionally used CoSi seems to reach its ultimate limits. For the gate length below 40 nm gate sheet resistance increases dramatically (Fig. 7), which is related to silicide instability and silicide cracking. No improvement is observed when Co is alloyed with Ni. Besides, high Si consumption during the silicide process leads to unacceptable increase in the junction leakage. Therefore, other materials such as NiSi or PtSi were considered as potential candidates for 65 nm technology node [9].

Fig. 7. Gate sheet resistance of Co and CoNi silicided gate as a function of the gate length.

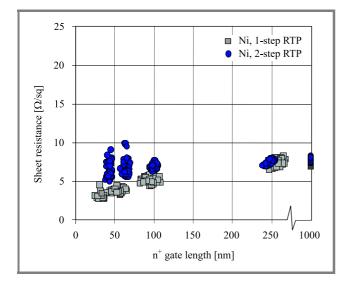

For Ni-silicided poly gates low sheet resistance is obtained down to the narrowest line widths (Fig. 8). The trade-off between junction leakage and silicide sheet resistance is

Fig. 8. Gate sheet resistance of Ni silicided gate processed with different annealing steps as a function of the gate length.

in favour of Ni-silicide. Besides, NiSi is known to have smaller contact resistance, which has significant role in total resistance of the junctions in sub-50 nm devices.

## 6. Conclusions

Conventional bulk scaling reaches its physical limitations. The 65 nm CMOS appears to be the last technology node, where the conventional planar transistor architecture in conjunction with standard modules will be applied. In order to maintain the trend in performance improvement, next technology generations will probably have to deal with more exotic solutions such as strained silicon, metal gate integration, high-*k* dielectrics (mainly for low power applications) and eventually double gate architectures.

### References

- International Technology Roadmap for Semiconductions, 2001, http://public.itrs.net/Files/2001ITRS/Home.htm

- [2] F. N. Cubaynes, J. Schmitz, C. van der Marel, H. Snijders, A. Veloso, and A. Rothschild, "Plasma nitridation optimization for sub-1 A gate dielectrics", in *ECS Symp.*, Paris, France, 2003.

- [3] A. Veloso, F. N. Cubaynes, A. Rothschild, S. Mertens, R. De-graeve, R. O'Connor, C. Olsen, L. Date, M. Schaekers, C. Dachs, and M. Jurczak, "Ultra-thin oxynitride gate dielectrics by pulsed-RF DPN for 65 nm general purpose CMOS applications", in *Conf. ESSDERC'03*, Lisbon, Portugal, 2003.

- [4] R. O'Connor, R. Degraeve, B. Kaczer, A. Veloso, G. Hughes, and G. Groeseneken, "Weilbull slope and voltage acceleration of ultra-thin (1.1–1.45 nm EOT) oxynitrides", in *Conf. INFOS'03*, Stará Lesná, Slovakia, 2003.

- [5] L. Van den Hove, M. Goethals, K. Ronse, M. Van Bavel, and G. Vandenberghe, "Lithography for sub-90 nm applications", in *IEDM Tech. Dig.*, San Francisco, USA, 2002, pp. 3–8.

- [6] R. Lindsay, B. Pawlak, J. Kittl, K. Henson, C. Torregiani, S. Giangrandi, R. Surdeanu, W. Vandervorst, A. Mayur, J. Ross, S. McCoy, J. Gelpey, P. Stolk, and K. Maex, "A comparison of spike, flash, SPER and laser annealing for 45 nm CMOS", in *MRS Symp.*, Paris, France, 2003.

- [7] B. J. Pawlak, R. Lindsay, R. Surdeanu, X. Pages, W. Vandervorst, and K. V. D. Jeugd, "The role of F with Ge pre-amorphisation in forming PMOS junctions for the 65 nm CMOS technology node", in ECS Symp., Paris, France, 2003.

- [8] R. Lindsay, B. J. Pawlak, J. Kittl, K. Henson, S. Giangrandi, R. Duffy, R. Surdeanu, W. Vandervorst, P. Stolk, and K. Maex, "Leakage optimisation of ultra-shallow junctions formed by solid phase epitaxial regrowth (SPER)", *Proc. J. Vac. Sci. Technol*, vol. B, Febr. 2003.

- [9] A. Lauwers, J. Kittl, A. Akheyar, M. Van Dal, O. Chamirian, M. de Potter, R. Lindsay, and K. Maex, "Silicide scaling: Co, Ni or CoNi?", in ECS Symp., Paris, France, 2003.

Małgorzata Jurczak received M.Sc. and Ph.D. degrees in electrical engineering from the Warsaw University of Technology (WUT), Poland, in 1991 and 1997. In 1991 she joined WUT, where she worked on modelling of MOS SOI devices. In 1994 she was with NMRC, Cork, Ireland, and in 1997 with Kyung Hee University, Seoul,

Korea. In 1998 she joined CNET Grenoble, France Telecom. She was involved in development of 0.18 and 0.12  $\mu$ m CMOS process and alternative approaches for sub-0.1  $\mu$ m CMOS. In 2000 she joined IMEC, Leuven, Belgium. In the years 200-2003 she was the IMEC coordinator of the JDP program with Philips on device process integration for 90 nm and 65 nm CMOS. From 2003 she has been the group leader of the CMOS Device Implementation Projects (45 nm CMOS, FUSI gate, strained Si, HK+MG integration, FD SOI, MUGFET). She is also a project manager of IMEC Industrial Affiliation Program (IIAP) on ultimate devices EMERALD. She has participated in several European projects: ACE, ULTRA, MEDEA, HUNT. She was the project coordinator of the European IST ARTEMIS project. Currently she is in the Technical Advisory Committee of the IST Integrated Project NanoCMOS. She holds 15 French and American patents and authored and co-authoured more than 60 papers. She has been a member of scientific committee of IEDM (in 2002 and 2003) and ESSDERC conferences (2000, 2004 and 2005). She received the Best Paper Award at ESSDERC'2000 Conference and the Paul Rappaport Award for the best paper published in IEEE TED

e-mail: malgorzata.jurczak@imec.be IMEC Kapeldreef st 75 3001 Leuven, Belgium

Anabela Veloso, Rita Rooyackers, Emmanuel Augendre, Sofie Mertens, Aude Rotschild, Marc Scaekers, Richard Lindsay, Anne Lauwers, Kirklen Henson, Simone Severi, Ivan Pollentier, An de Keersgieter IMEC

Kapeldreef st 75 3001 Leuven, Belgium