# JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

### Preface

Despite the fact that a range of limitations are beginning to appear as CMOS technology is being raised to ever higher levels of perfection, it is anticipated that silicon will be the dominant material of the semiconductor industry for at least the first half of the 21st century. The forecast for microelectronics development published in 2006 by Semiconductor Industry Association (SIA) reaches ahead to the years 2014–2020. Moreover, a comparison with former SIA forecasts indicates that they become more aggressive (that is more optimistic) with time.

While the development of silicon microelectronics in the past could be attributed mostly to the reduction of the feature size (progress in lithography), today it relies more on new material solutions, such as SOI, SON, SiGe or SiC. The combination of this trend with continuous miniaturization provides the opportunity of improving IC functionality and speed of operation.

Telecommunications and information technology are arguably the most powerful drivers behind microelectronics product development nowadays. Plenty of new applications are being created for fast analog and rf circuits, as well as for information processing ones. It is clear that with the anticipated peak  $f_{\rm max}=425$  GHz and  $f_T=385$  GHz to be reached by rf SiGe-base bipolar transistors in 2011, according to the 2006 issue of ITRS, a lot of effort must be put into the development of appropriate material, processing, characterization and modeling. While progress in the bipolar technology is impressive, the increase of MOSFET speed is even more so. The same issue of ITRS predicts on-chip clock of 73 GHz for 2020, which will require MOSFET internal switching speed of 12 500 GHz.

High-speed isn't, however, everything. Portable wireless products push, for obvious reasons, for low-power solutions. This trend requires new architectural solutions (e.g., channel thinning), and in consequence, new material, such as SOI (or its possible successor SON), where current driveability is considerably higher than in conventional MOSFETs.

In this issue the Reader will find the invited lectures presented during the 7th Symposium Diagnostics & Yield: Advanced Silicon Devices and Technologies for ULSI Era, which took place at Warsaw University of Technology on June 26–28, 2006. A number of the papers are devoted to advanced materials, such as SOI, SiC and SiGe and the most important issues concerning semiconductor technology (difficulties faced by CMOS technology, gate-dielectric

fabrication, wafer-cleaning problems). Several papers address also semiconductor structure characterization (DC and noise analysis, wideband characterization) and modeling (negative bias temperature instability).

We hope the Readers will find this issue useful and interesting.

Organization of this Symposium would not be possible without the support of SINANO – a Network of Excellence funded by the European Commission under the 6th Framework Programme (EC contract no. 506844) and Polish Ministry of Science and Higher Education (research projects no. 3T11B 012 28, 3T11B 020 30). The organizers are also grateful to the National Institute of Telecommunications for making this *Journal* available for the publication of the Symposium papers.

Andrzej Jakubowski Lidia Łukasiak Guest Editors Invited paper

# SOI nanodevices and materials for CMOS ULSI

Francis Balestra

Abstract— A review of recently explored new effects in SOI nanodevices and materials is given. Recent advances in the understanding of the sensitivity of electron and hole transport to the tensile or compressive uniaxial and biaxial strains in thin film SOI are presented. The performance and physical mechanisms are also addressed in multi-gate Si, SiGe and Ge MOSFETs. The impact of gate misalignment or underlap, as well as the use of the back gate for charge storage in double-gate nanodevices and of capacitorless DRAM are also outlined.

Keywords— ballistic transport, gate misalignment, GIFBE, mobility enhancement, SOI, strain engineering, tunneling current.

#### 1. Introduction

The silicon-on-insulator (SOI) devices are the best candidates for the ultimate integration of ICs on silicon. The flexibility of the SOI structure and the possibility to realize new device architectures allow optimum electrical properties to be obtained for low power and high performance circuits. These transistors are also very interesting for high frequency and memory applications [1–3]. In this paper, an overview of recently explored new effects in advanced SOI devices and material is given. The advantages and drawbacks of a number of new device architectures are also addressed.

## 2. Physical mechanisms in advanced SOI MOSFETs

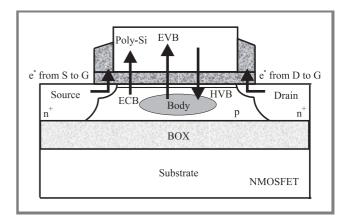

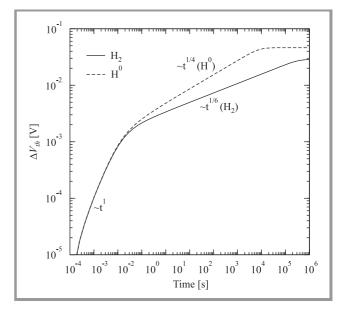

Ultra-thin gate oxide (sub-2 nm) leads to direct gate tunneling currents [4] that consist of three main streams of carriers (Fig. 1). In partially-depleted (PD) SOI MOSFETs, the floating body of the device is isolated by the buried oxide (BOX) and charged by the direct tunneling currents,  $J_{EVB}$  and  $J_{HVB}$ . When a floating-body device is biased in inversion, the body is mainly charged by a hole current resulting from the tunneling of valence band electrons into the gate ( $J_{HVB} \ll J_{EVB}$ ). When biased in accumulation, the body is charged with electrons coming from the gate conduction band. These currents strongly affect the body potential of the PD devices, giving rise to gate-induced floating body effect (GIFBE). The different gate current contributions are plotted in Fig. 1 to illustrate the body-charging mechanism.

A direct consequence of the GIFBE is the sudden increase of the drain current characteristics for  $V_G$  close to 1.1 V.

*Fig. 1.* Tunneling current components in a NMOSFET. Explanations: EVB – valence band electron tunneling, ECB – conduction band electron tunneling, HVB – valence band hole tunneling.

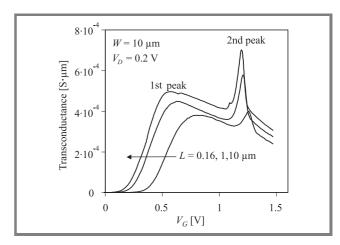

For this voltage, the gate-to-body current  $(I_{GB})$  charges up the body and the drain current increases. This "kink-like" effect gives rise to a strong second peak in transconductance (up to 40% increase), which clearly appears in Fig. 2 for low drain bias. This figure illustrates the in-

Fig. 2. Normalized transconductance of a 10  $\mu$ m wide NMOS-FET versus gate bias for various gate lengths.

fluence of the gate size on the GIFBE's amplitude and position. The voltage corresponding to the onset of the 2nd peak of transconductance  $(G_m)$  is nearly independent of the gate length (and width) whereas the amplitude of the peak depends on the device geometry. The 2nd peak is clearly reduced as the gate length (or width) are shrunk down. It is usually reported that floating body effects (FBEs) are reduced in short-channel devices by enhanced junction leakage or in narrow-channel devices by

increased recombination rate near the sidewalls. In both cases, the removal of majority carriers from the body is more efficient, hence the body charging by  $I_{GB}$  is less effective and the GIFBE is reduced. However, even in the smallest transistor, where both junction and sidewall contributions occur, the role of the gate tunneling current remains significant.

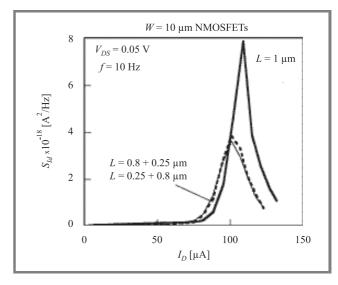

The drain power spectral density also presents a special behavior [4]. For  $V_G$  values inferior to the GIFBE onset gate voltage (around 1.1–1.2 V), conventional 1/f noise is observed, attributed to carrier fluctuations from the inversion layer due to carrier trapping/detrapping in the vicinity of the silicon/SiO<sub>2</sub> interface. Nevertheless, an excess noise occurs, characterized by the superposition of a Lorentzian-like component on the 1/f noise when the GIFBE is present. Similarly to FB PD SOI devices in saturation mode, a flat plateau is followed by a  $1/f^2$  roll-off at a given corner frequency. In this case, the corner frequency shifts to higher frequencies as the drain bias increases: here, the front gate bias plays the role of the drain bias, and we have a similar behavior with frequency as the Kink-related excess noise.

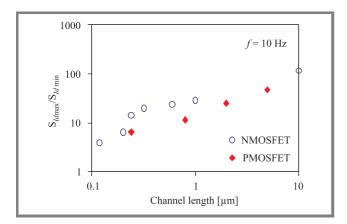

From more than two decades for  $L=10~\mu m$ , the excess noise decreases down to only one decade or less, and becomes almost insignificant for short devices (L=0.20, 0.12  $\mu m$ ). Figure 3 represents the calculated ratio between the maximum drain current power spectral density ( $S_{Id\,max}$ ) and the minimum one ( $S_{Id\,min}$ , value of the plateau at low  $V_G$  without GIFBE).

*Fig. 3.* Ratio between the maximum drain current noise ( $S_{Id\,\text{max}}$ ) and the minimum one ( $S_{Id\,\text{min}}$ , value of the plateau at  $V_G=0.9~\text{V}$ ) for N- and PMOSFETs.

Two general features may explain the obtained results. On the one hand, the magnitude of the second transconductance peak is reduced as the channel length is shortened (FBEs are usually lowered by enhanced contributions from junctions), and the role of the gate current is partially offset, so that we notice a reduced contribution of the  $G_m$  2nd peak on the noise overshoot. On the other hand, reducing the channel length causes an enhancement of the 1/f noise level, and this higher noise level probably masks the excess noise due to the GIFBE.

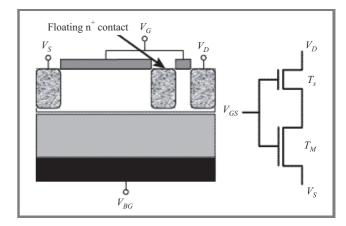

The GIFBE in a twin-gate (TG) structure (Fig. 4) is significantly reduced [5].

Fig. 4. Twin-gate NMOSFET.

In particular, the impact of the TG structure is pronounced on the Lorentzian noise overshoot (Fig. 5). Such a reduction results from a lowering of the part of the EVB current that reaches the source junction (the holes from the slave part ( $T_s$ ) of the TG device are screened from reaching the source by recombination at the inner  $n^+$  contact).

*Fig.* 5. Spectral density of drain current noise  $(S_{Id})$  versus drain current  $(I_D)$  for NMOSFET (bold line) compared with the two TG combinations.

A GIFBE is also observed in fully depleted FinFET when a back gate bias is applied leading to an accumulation at the bottom of the fin (Fig. 6) [6].

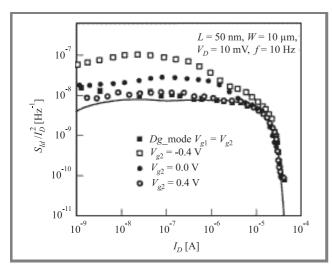

In a double gate MOSFET, the application of a back gate voltage can lead to a volume inversion and to a screening reducing the number of trapped carriers in the gate oxides. This phenomenom induces a reduction of the low frequency noise (Fig. 7) [7].

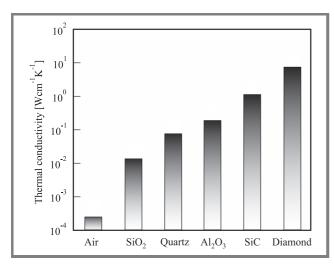

The self-heating effect is also a harmful parasitic effect in SOI. The traditional buried silicon dioxide has a poor thermal conductivity that leads to an enhancement of the chan-

*Fig.* 6. Measured transconductance of a FD FinFET for different values of back gate bias ( $L=10~\mu m$ ).

*Fig.* 7. Normalized drain current noise of a double gate NMOS-FET for different back gate biases. Solid line:  $S_{VG} (G_m/I_D)^2$  for double gate mode.

Fig. 8. Thermal conductivity of various buried oxide materials.

nel temperature and thus a reduction of carrier mobilities and drain current. The thermal conductance of various buried insulator materials is shown in Fig. 8 [8]. As it is shown in this figure, many insulators have a better thermal conductivity compared to  $SiO_2$ . In addition, diamond and quartz are also best suited dielectrics for controlling short channel effects and therefore to replace  $SiO_2$ . SiC and  $Al_2O_3$  needs the use of thin buried insulator together with a ground plane architecture.

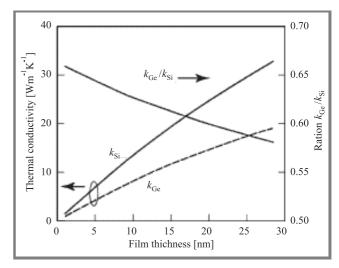

On the other hand, it is worth noting that the thermal conductivity of Ge films is lower than that of Si films for bulk materials (Fig. 9) [9]. However, for ultra-thin films,

Fig. 9. Estimated thermal conductivity of thin Si and Ge layers.

*Fig. 10.* Drain current degradation measured at  $V_{GT} = 0.5$  V and  $V_D = 50$  mV for various NMOSFET architectures in the worst-case aging scenario (aging conditions:  $V_G = V_D = 2.2$  V).

these values are very close and therefore Ge films will present similar self-heating (SH) effects as Si films for deep sub-0.1  $\mu$ m devices realized on nanometric layers.

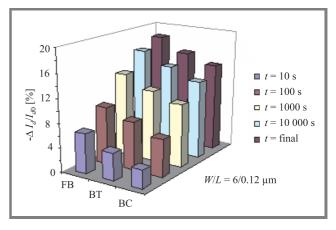

Hot carrier effects are limiting long term device reliability. In SOI structures, special hot carrier regimes exist. Figure 10 shows the relative degradation of the drain current for various PD device architectures: floating body (FB), body connected (BC) and body tied (BT) [4]. This figure

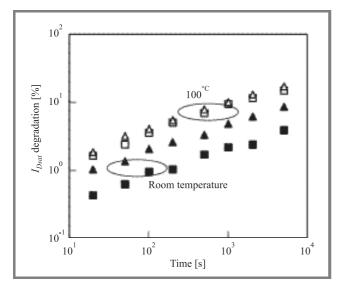

Fig. 11. Channel-width dependence of hot-carrier-induced degradation at room and high temperatures (squares – narrow, triangles – wide).

is plotted for the worst case aging in advanced SOI devices (maximum gate current,  $V_G = V_D$ ). Body connected devices exhibit enhanced hot carrier immunity because of the collected hole coming from the impact ionization at the drain edge. Device degradation is also lowered for narrow channels due to reduced floating body effects (Fig. 11) [10].

## 3. Influence of strain and surface orientation on the electrical properties of thin layers on insulators

Compressive and tensile biaxial and uniaxial stress silicon technologies are promising for enhancing CMOS performance in bulk and SOI MOSFETs. The combination of strained layers and ultra thin films SOI structures is one of the best candidates for decananometer MOSFETs.

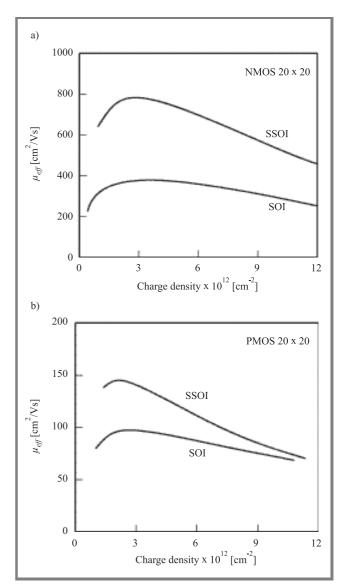

Figure 12 is a plot of the dependence of electron and hole mobilities as a function of the charge density [11]. The strained Si layer is fabricated with sacrificial thin relaxed SiGe and smart cut. In the SSOI devices, substantial enhancements of both electron (about 100%) and hole (about 50%) mobilities are obtained compared with the control SOI device at intermediate charge densities for long channel transistors.

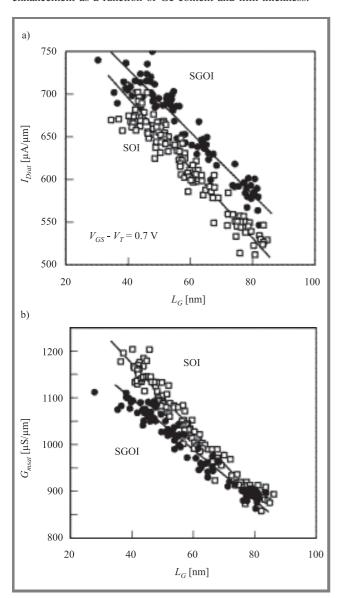

An enhancement of the electron mobility of about 15–20% has been obtained for short channels (70 nm technology) SGOI MOSFETs (strained Si-on-SiGe-on-insulator) together with superior short channel control [12, 13]. Figure 13 shows the enhancement of the drain current for sub-0.1  $\mu$ m devices.

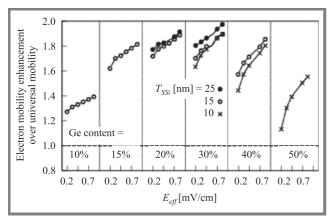

In Fig. 14, the electron mobilities are represented for various Ge content of the SiGe layer and different Si film thicknesses. The electron mobility enhancement is max-

Fig. 12. Effective mobility comparison between SSOI and SOI MOSFETs: (a) electron mobility; (b) hole mobility.

Fig. 13.  $I_D$ – $V_D$  characteristics of 70 nm MOSFETs ( $W=1~\mu m$ ).

*Fig. 14.* Effective-field  $(E_{eff})$  dependence of electron mobility enhancement as a function of Ge content and film thickness.

Fig. 15. Comparison of  $I_{Dsat}$  (a) and  $G_{msat}$  (b) at a constant gate overdrive.

imum for 30% of Ge due to the increase in alloy scattering and/or surface roughness for higher Ge concentra-

tions and the hole mobility continuously increases with Ge up to 50% [13]. It is also worth noting that the enhancement of carrier mobility is reduced in thinner strained Si films due to interface states and fixed charges induced by the diffusion of Ge atoms to the interfaces.

Figure 15 shows  $I_{Dsat}$  and  $G_{msat}$  as a function of channel length for SGOI and SOI MOSFETs. An enhancement of  $I_D$  is outlined down to sub-50 nm transistors for SGOI, but the difference diminishes at smaller channel lengths due in particular to larger SH in SiGe than in Si. This SH effect in SGOI degrades  $G_{msat}$ , which is more sensitive to SH than  $I_D$ . Therefore the transconductance appears degraded in SGOI as compared to SOI but after correction of the self-heating a similar increase is obtained for  $I_D$  and  $G_m$  in the SGOI structure [14].

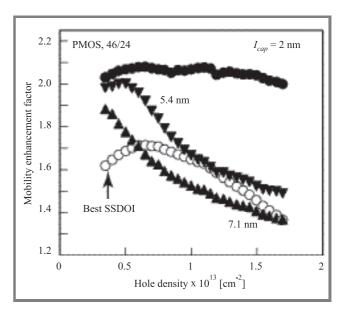

The HOI structure (strained Si/strained SiGe/ strained Si heterostructure-on-insulator) presents also substantial electron and hole mobility enhancements [15]. In particular, hole mobilities are very high for thin Si cap layer (enhancement of about 100%) compared with the universal SOI mobility and are also significantly higher that the best SSDOI mobility (strained Si directly-on-insulator) due to the compressively strained buried SiGe channel (Fig. 16).

*Fig. 16.* Mobility enhancement in HOI compared with the best SSDOI curve relative to the universal SOI mobility.

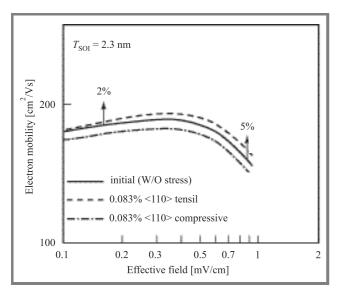

Uniaxial strain engineering is also useful for mobility enhancement for Si film thickness in the sub-10 nm range [16]. A similar enhancement of electron mobility in 3.5 nm SOI devices under biaxial and uniaxial tensile strain has been obtained. The electron mobility is also enhanced in 2.3 nm Si layer under uniaxial tensile strain (Fig. 17), and the hole mobility increases in 2.5 nm film under uniaxial compressive strain.

It has recently been shown that the use of a metal gate (TiN) can induce significant compressive stress along the channel direction. This stress is increased as the gate length decreases. This phenomenon progressively degrades electron

mobility while hole transport is improved. Similar behaviors are obtained in single and double gate SOI devices, and the use of  $\langle 110 \rangle$  channel orientation is the most favorable in terms of electrical performance [17].

*Fig. 17.* Electron mobility in 2.3 nm ultra-thin-body MOSFET under  $\langle 110 \rangle$  uniaxial strain.

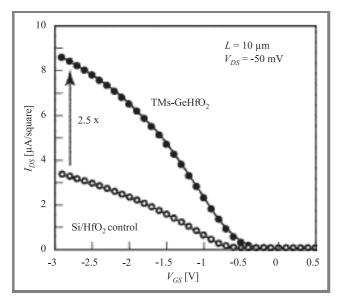

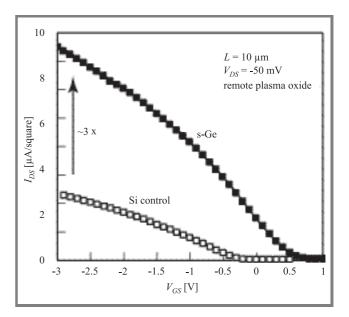

Pure Ge channel MOSFETs are also considered as one promising option for future high performance CMOS. A compressively strained Ge channel is expected to further enhance hole mobility due to the very small effective

*Fig. 18.* Drain current of PMOSFETs with HfO<sub>2</sub> gate oxide on 60% Ge channel formed by local thermal mixing compared with Si PMOS control with HfO<sub>2</sub>.

hole mass [18]. Figure 18 shows the linear current of s-Ge PMOS with  $HfO_2$  gate dielectrics along with the Si control device. A 2.5 × performance enhancement is observed (similar enhancement for the transconductance). For s-Ge

*Fig. 19.* Drain current of PMOSFETs with remote plasma oxide on 100% Ge channel formed by selective UHVCVD compared with Si channel PMOS control with the same oxide.

*Fig. 20.* Simulated surface-roughness limited hole mobility for Si (a) and Ge (b) with various orientations. Hole density  $5 \cdot 10^{11}$  cm<sup>-2</sup>.

P-type devices with  $SiO_2$  gate oxide, a 3 × drive current and transconductance is obtained (Fig. 19).

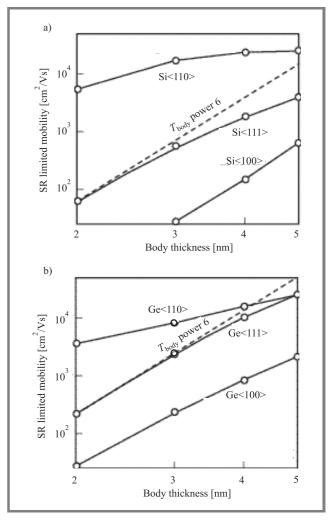

The influence of surface-roughness (SR) in ultra-thin films is very important. Figure 20 shows the SR limited hole mobility as a function of body thickness for Si (SOI) and Ge (GOI) channels. The variation of hole mobility is outlined for various surface orientations [19].

*Fig. 21.* Electron mobility of FinFETs with  $\langle 100 \rangle$  and  $\langle 110 \rangle$  fin orientation.  $T_{ox} = 2$  nm,  $4.5 \cdot 10^{13}$  cm<sup>-2</sup> channel implantation.

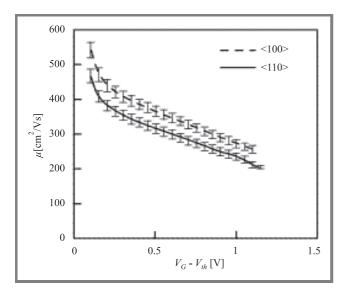

Figure 21 represents electron mobilities in FinFETs with various fin orientations. An improvement of electron mobility is observed for  $\langle 100 \rangle$  and an enhancement of hole mobility has also been shown for  $\langle 110 \rangle$  orientation [20].

## 4. Comparison of the performance and physical mechanisms in multi-gate devices

Multi-gate MOSFETs realized on thin films are the most promising devices for the ultimate integration of MOS structures due to the volume inversion in the conductive layer [21].

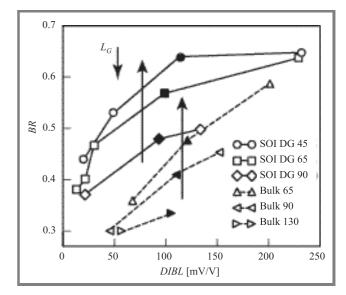

The on-current  $I_{on}$  of the MOSFET is limited to a maximum value  $I_{BL}$  that is reached in the ballistic transport regime. Figure 22 reports the self-consistent Monte Carlo (MC) simulation of the ballistic ratio  $BR = I_{on}/I_{BL}$  versus drain induced barrier lowering (DIBL) showing that one can increase the BR by scaling the gate length, thus increasing the longitudinal field at the source, but this comes at the cost of a larger DIBL. For a given DIBL, an increased ballisticity is obtained for low doping double gate SOI devices [22].

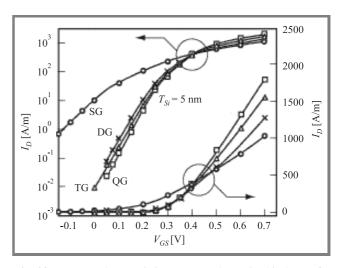

The transfer characteristics of several multiple-gate (1, 2, 3 and 4 gates) MOSFETs, calculated using the 3D Schrödinger-Poisson equation and the non-equilibrium Green's function formalism for the ballistic transport or MC simula-

*Fig. 22.* Ballisticity ratio at  $V_G = V_D = V_{DD}$  versus *DIBL*. Filled symbols represent transistors with the nominal gate length for the high-performance MOSFET of each technology node.

*Fig. 23.*  $I_D$ – $V_{GS}$  characteristics at  $V_{DS} = 0.7$  V in thin layers for different multi-gate architectures.

tions, have shown similar trends. The best performance (drain current, subthreshold swing) is outlined for the 4-gate (QG or GAA) structure [23, 24] (Fig. 23).

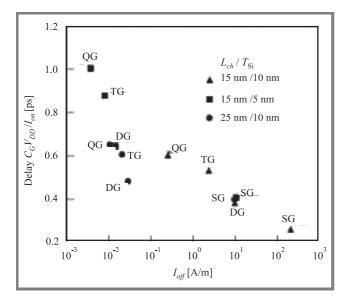

However, Fig. 24 demonstrates that the propagation delay in triple gate (TG) and quadruple gate (QG) MOSFETs are degraded due to a strong rise of the gate capacitance. A properly designed double-gate (DG) structure appears to be the best compromise at given  $I_{off}$  [24].

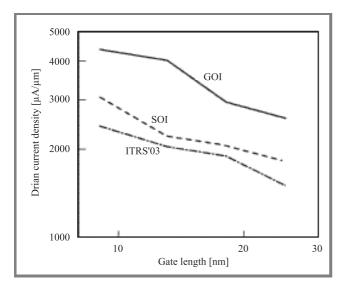

Figure 25 compares the calculated ballistic drive current for Si and Ge double-gate MOSFETs at the operation point of each generation as predicted by International Technology Roadmap for Semiconductors (ITRS) [25]. Si barely satisfies the ITRS requirement, whereas Ge offers much higher current drive. However, the simulated value of the real drain current of 2G SOI transistors is not able to satisfy the ITRS objectives, even for intrinsic devices without

*Fig. 24.* Propagation delay versus  $I_{off}$  for single-gate and multigate SOI devices.

Fig. 25. Ballistic drive current for different technology nodes for SOI and GOI devices.

parasitic S/D resistances. The 2G GOI MOSFETs are able to provide the needed current drive, but parasitic resistances drastically affect the drain current (not shown here).

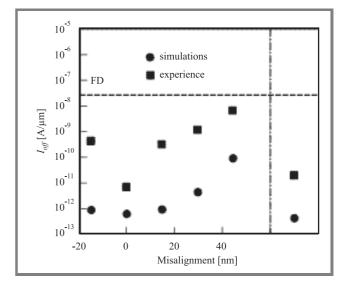

For a double gate device, the impact of a gate misalignment on the leakage current is important. This current is mainly due to gate induced leakage current (GIDL). This off-current is enhanced with increasing the misalignment and it is higher for a shift of the bottom gate towards the drain due to a higher  $V_{GD}$  compared to  $V_{GS}$  [26].

The impact of a gate misalignment is also significant for  $I_{on}$  in 2G MOSFETs [27]. A large back gate (BG) shift reduces the saturation current compared to the aligned case, whereas a slight BG shift towards the source increases  $I_{on}$ . This is due to a lower source access resistance. In terms of short channel effects, aligned transistors exhibit the best

control while highly misaligned MOSFETs operate like single gate ones. The off-current  $I_{off}$  is much more influenced by the misalignment than  $I_{on}$  due to a degradation of the electrostatic control (Fig. 26). The oversized transistor shows attractive static performance (right hand side of Fig. 26) and a better tolerance to misalignment but the dynamic performance is rapidly degraded as the overlap length increases.

*Fig. 26.* Evolution of  $I_{off}$  with misalignment (experimental and simulations results,  $V_D = 1.2$  V). Single gate FD results are represented by a dashed line.

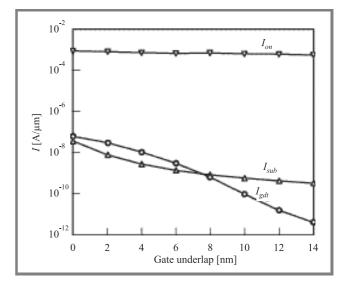

*Fig.* 27.  $I_{on}$ , subthreshold  $(I_{sub})$  and gate direct tunneling  $(I_{gdt})$  currents as a function of gate underlap.

In decananometer MOSFETs, gate underlap is a promising solution in order to reduce the *DIBL* effect. Figure 27 presents the variations of the driving current, the subthreshold current and the gate direct tunneling current versus gate underlap [28]. The on-current is almost not affected by

the gate underlap whereas the leakage currents are substantially reduced due to a decrease in DIBL and drain to gate tunneling current. A reduction of the effective gate capacitance  $C_G$  for larger underlap values at iso  $I_{on}$  has also been shown. This reduction of  $C_G$  leads to a decrease in the propagation delay and power.

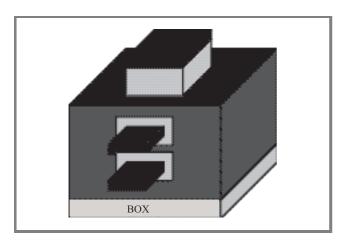

Multi-bridge-channel MOSFETs (MBCFET) also present very high performance better than that of gate-all-around (GAA) devices and exceeding the ITRS roadmap requirements (Fig. 28) [29].

Fig. 28. Schematic diagram of MBCFET on SOI.

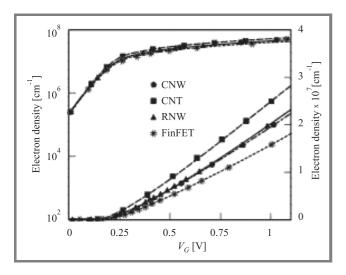

*Fig. 29.* Electron density per unit length for various devices (FinFET, nanowires and carbon-nanotube FET). 65 nm technology node data (EOT = 0.9 nm,  $T_{Si} = 5 \text{ nm}$ ).

Finally, FinFETs are compared with cylindrical (CNW) and rectangular (RNW) nanowires and also with gate-all-around carbon nanotubes (CNT) FET. It is shown that the CNTFET exhibits superior performance (Fig. 29) due to electron charge confinement at the surface of the nanotube, whereas in the Si-based nanowires the charge confinement at the center of the wire is responsible for an additional depletion capacitance in series with the oxide capacitance, which reduces the overall effectiveness of the gate [30].

## 5. Advanced SOI dynamic and non-volatile RAM

It is becoming difficult for memories to be scaled down. Indeed, traditional embedded dynamic random-access memory (DRAM) requires a complicated stack capacitor or a deep trench capacitor in order to obtain a sufficient storage capacitance in smaller cells. This leads to more process steps and thus less process compatibility with logic devices.

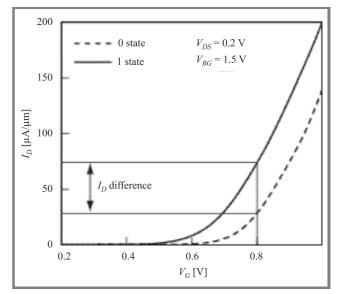

Capacitor-less 1T-DRAM or floating body cells have shown promising results. The operation principle is based on excess holes which can be generated either by impact ionization or by gate-induced leakage current in partially-depleted SOI MOSFETs. The GIDL current is due to band-to-band tunneling and occurs in accumulation leading to a low drain current writing and reduced power consumption together with a high speed operation. However, conventional PD SOI MOSFETs require high channel doping to suppress short-channel effects, which induces a degradation in retention characteristics. In order to overcome this problem, a DG-FinDRAM has been proposed showing superior memory characteristics (Fig. 30) [31].

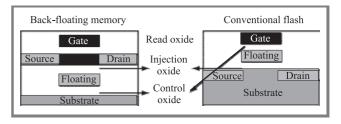

Conventional floating-gate flash memory has also scaling difficulties due to nonscaling of gate-insulator stack and inefficient hot carrier injection processes at sub-50 nm gate

Fig. 30.  $I_D$ – $V_G$  characteristics of the DG-FinDRAM.

Fig. 31. Cross-sections of back floating gate and conventional front-floating gate memories.

dimensions. Back-floating gate flash memory overcomes these limitations by decoupling read and write operations and independent positioning and/or sizing of the storage element (back-floating gate) under the Si channel (Fig. 31). The charge in the back gate affects the field and the potential at the bottom interface and thus changes the threshold voltage of the device. The back-floating gate is charged by applying  $-10~\rm V$  to the source, the drain and the front gate simultaneously, and the charges are removed from the back floating gate (erasing) with the same method but with a bias of  $+10~\rm V$  [32].

#### 6. Conclusion

In this paper, a review of recently explored new effects in advanced SOI devices and materials has been given. The impact of key device parameters on electrical and thermal floating body effects has been addressed for various device architectures. Recent advances in the understanding of the sensitivity of electron and hole transport to the tensile or compressive uniaxial and biaxial strains in thin film SOI have been shown. The performance and physical mechanisms have also been presented in multi-gate MOS-FETs. New hot carrier phenomena have been discussed. The impact of gate misalignment or underlap, as well as the use of the back gate for charge storage in double-gate nanodevices and of capacitorless DRAM have also been outlined.

#### Acknowledgements

This work was partially supported by the European Network of Excellence SINANO (Silicon-based Nanodevices, FP6, IST-1-506844-NE).

#### References

- J. P. Colinge, Silicon-on-Insulator Technology: Materials to VLSI. Boston: Kluwer, 1991.

- [2] S. Cristoloveanu and S. S. Li, Electrical Characterization of Siliconon-Insulator Materials and Devices. Boston: Kluwer, 1995.

- [3] F. Balestra, SOI Devices. Encyclopedia of Electrical and Electronics Engineering. New York: Wiley, 1999.

- [4] F. Dieudonné, S. Haendler, J. Jomaah, and F. Balestra, "Gate-induced floating body effect, low frequency noise and hot carrier reliability in advanced SOI MOSFETs", Solid-State Electron., vol. 48, issue 6, pp. 985–997, 2004.

- [5] E. Simoen et al., "Electron valence-band tunneling excess noise in twin-gate silicon-on-insulator MOSFETs", in Proc. ULIS'2005, Bologna, Italy, 2005, p. 113.

- [6] W. Xiong et al., "Full/partial depletion effects in FinFETs", in Proc. IEEE Int. SOI Conf., Charleston, USA, 2004, p. 195.

- [7] L. Zafari et al., "On the low frequency noise in fully depleted and double-gate SOI transistors", in *Proc. ULIS* 2005, Bologna, Italy, 2005, p. 147.

- [8] N. Bresson et al., "Alternative dielectrics for advanced SOI MOS-FETs: thermal properties and short channel effects", in Proc. IEEE Int. SOI Conf., Charleston, USA, 2004, p. 62.

- [9] E. Pop et al., "Electro-thermal comparison and performance optimization of thin-body SOI and GOI MOSFETs", in *Proc.* IEDM'2004, San Francisco, USA, 2004, p. 411.

- [10] D. P. Ioannou et al., "New insights on the hot-carrier characteristics of 55 nm PD SOI MOSFETs", in Proc. IEEE Int. SOI Conf., Charleston, USA, 2004, p. 205.

- [11] J. J. Lee et al., "Mobility enhancement of SSOI devices fabricated with sacrificial thin relaxed SiGe", in Proc. IEEE Int. SOI Conf., Charleston, USA, 2004, p. 139.

- [12] M. Sadaka et al., "Fabrication and operation of sub-50 nm strained-Si on Si<sub>1-x</sub>Ge<sub>x</sub> on insulator (SGOI) CMOSFETs", in Proc. IEEE Int. SOI Conf., Charleston, USA, 2004, p. 209.

- [13] T. Numata et al., "Performance enhancement of partially- and fully-depleted strained-SOI MOSFETs and characterization of strained-Si devices parameters", in *Proc. IEDM'04*, San Francisco, USA, 2004, p. 177.

- [14] J. Cait et al., "Performance comparison and channel length scaling of strained Si FETs on SiGe-on-insulator (SGOI)", in Proc. IEDM'04, San Francisco, USA, 2004, p. 165.

- [15] I. Aberg et al., "High electron and hole mobility enhancements in thin-body strained Si/strained SiGe/strained Si heterostructures on insulator", in Proc. IEDM'2004, San Francisco, USA, 2004, p. 173.

- [16] K. Uchida et al., "Experimental study of biaxial and uniaxial strain effects on carrier mobility in bulk and ultra-thin-body SOI MOS-FETs", in Proc. IEDM'2004, San Francisco, USA, 2004, p. 229.

- [17] T. Guillaume et al., "Influence of the mechanical strain induced by a metal gate on electron and hole transport in single and doublegate SOI MOSFETs", in *Proc. IEEE Int. SOI Conf.*, Charleston, USA, 2004, p. 42.

- [18] H. Shang, "Selectively formed high mobility strained Ge PMOSFETs for high performance CMOS", in *Proc. IEDM'2004*, San Francisco, USA, 2004, p. 157.

- [19] T. Low, "Impact of surface roughness on silicon and germanium ultra-thin-body MOSFETs", in *Proc. IEDM'2004*, San Francisco, USA, 2004, p. 151.

- [20] E. Landgraf et al., "Influence of crystal orientation and body doping on trigate transistor performance", in *Proc. ULIS* 2005, Bologna, Italy, 2005, p. 15.

- [21] F. Balestra et al., "Double-gate silicon-on-insulator transistor with volume inversion: a new device with greatly enhanced performance", IEEE Electron Dev. Lett., vol. EDL-8, p. 410, 1987.

- [22] S. Eminente et al., "Enhanced ballisticity in nano-MOSFETs along the ITRS roadmap: a Monte Carlo study", in Proc. IEDM'2004, San Francisco, USA, 2004, p. 609.

- [23] M. Bescond et al., "3D quantum modeling and simulation of multiple-gate nanowire MOSFETs", in Proc. IEDM'2004, San Francisco, USA, 2004, p. 617.

- [24] J. Saint-Martin, A. Bournel, and P. Dollfus, "Comparison of multiple-gate MOSFET architectures using Monte Carlo simulation", in *Proc. ULIS*'2005, Bologna, Italy, 2005, p. 61.

- [25] A. Khakifirooz, O. M. Nayfeh, and D. A Antoniadis, "Assessing the performance limits of ultra-thin double-gate MOSFETs: silicon vs. germanium", in *Proc. IEEE Int. SOI Conf.*, Charleston, USA, 2004, p. 79.

- [26] C. Yin and P. C. H. Chan, "Characterization and edge direct tunneling leakage of gate misaligned double gate MOSFETs", in *Proc. IEEE Int. SOI Conf.*, Charleston, USA, 2004, p. 91.

- [27] J. Widiez et al., "Experimental gate misalignment analysis on double gate SOI MOSFETs, in Proc. IEEE Int. SOI Conf., Charleston, USA, 2004, p. 185.

- [28] A. Bansal, B. C. Paul, and K. Roy, "Impact of gate underlap on gate capacitance and gate tunneling current in 16 nm DGMOS devices", in *Proc. IEEE Int. SOI Conf.*, Charleston, USA, 2004, p. 94.

- [29] E.-J. Yoon et al., "Sub-30 nm multi-bridge-channel MOSFET (MBCFET) with metal gate electrode for ultra high performance application", in Proc. IEDM'2004, San Francisco, USA, 2004, p. 627.

- [30] A. Marchi et al., "Investigating the performance limits of siliconnanowire and carbon-nanotube FETs", in Proc. ULIS'2005, Bologna, Italy, 2005, p. 99.

- [31] T. Tanaka, E. Yoshida, and T. Miyashita, "Scalability study on a capacitorless 1T-DRAM: from single-gate PD-SOI to doublegate FinDRAM", in *Proc. IEDM'2004*, San Francisco, USA, 2004, p. 919.

- [32] U. Avci, A. Kumar, and S. Tiwari, "Back-floating gate non-volatile memory", in *Proc. IEEE Int. SOI Conf.*, Charleston, USA, 2004, p. 133.

Francis Balestra was born in Digne, France, in 1960. He received the M.Sc. and Ph.D. degrees in electronics from the Institut National Polytechnique, Grenoble, France, in 1982 and 1985, respectively. In 1989, he obtained the habilitation diploma from the INPG authorizing him to supervise Ph.D. dissertations. He joined the

Laboratoire de Physique des Composants á Semiconducteurs (LPCS), INP Grenoble, in 1982, where he has been involved in research on the characterization, modeling, and simulation of the first fully depleted silicon-on-sapphire MOS transistors. He became Chargé de Recherche C.N.R.S. (Centre National de la Recherche Scientifique) in 1985 and Directeur de Recherche CNRS in 2000. In 1993–94, he joined the Research Center for Integrated Systems at Hiroshima University as a visiting researcher, and worked on sub-0.1  $\mu$ m MOSFETs and thin film SIMOX devices. Between 1996 and 1998 he has been Deputy Director of LPCS, Director of LPCS between 1999 and 2001,

and he is now Director of IMEP (Institute of Microelectronics, Electromagnetism and Photonics, INP Grenoble/CNRS/UJF) which is a Laboratory of 140 researchers and technical staff. He led several research teams on deep submicron CMOS, silicon on insulator devices, ultimate Si-based devices realized with innovating architectures, low temperature electronics and advanced bipolar transistors for BiCMOS technology. He has supervised over 15 research projects and 20 Ph.D. He has coordinated European, national and regional projects. He is presently coordinating a European Network of Excellence of the 6th Framework Programme dealing with Silicon-based Nanodevices (SINANO) with 44 European partners, which represents an unprecedented collaboration in this field in Europe. He was the organizer of many international conferences, e.g., the first (1994) and fifth (2002) European Workshop on Low Temperature Electronics (founder of WOLTE), the first (2000) and second (2001) European Conference on Ultimate Integration of Silicon (founder of ULIS), and of a NATO Advanced Research Workshop on SOI in 2000. He is a member of the Advisory Committee of the Chinese Journal of Semiconductors. Doctor Balestra is a member of the European Academy of Sciences since 2003 and got the Blondel Medal (French SEE) in 2001. He has coauthored over 100 publications in international scientific journals, 150 communications at international conferences (20 invited papers and review articles), and 15 books or chapters. e-mail: balestra@enserg.fr

Institut de Microélectronique, Electromagnétisme et Photonique

IMEP (CNRS-INPG-UJF)

INP Grenoble-Minatec

38016 Grenoble, France

Invited paper

# Special size effects in advanced single-gate and multiple-gate SOI transistors

Akiko Ohata, Romain Ritzenthaler, Olivier Faynot, and Sorin Cristoloveanu

Abstract— State-of-the-art SOI transistors require a very small body. This paper examines the effects of body thinning and thin-gate oxide in SOI MOSFETs on their electrical characteristics. In particular, the influence of film thickness on the interface coupling and carrier mobility is discussed. Due to coupling, the separation between the front and back channels is difficult in ultra-thin SOI MOSFETs. The implementation of the front-gate split C-V method and its limitations for determining the front- and back-channel mobility are described. The mobility in the front channel is smaller than that in the back channel due to additional Coulomb scattering. We also discuss the 3D coupling effects that occur in FinFETs with triple-gate and  $\Omega$ -gate configurations. In low-doped or tall fins the corner effect is suppressed. Narrow devices are virtually immune to substrate effects due to a strong lateral coupling between the two lateral sides of the gate. Short-channel effects are drastically reduced when the lateral coupling screens the drain influence.

Keywords— MOSFET, SOI, ultra-thin silicon, multiple-gate, mobility, coupling effect, thin gate oxide, gate-induced floating body effect, drain-induced virtual substrate biasing.

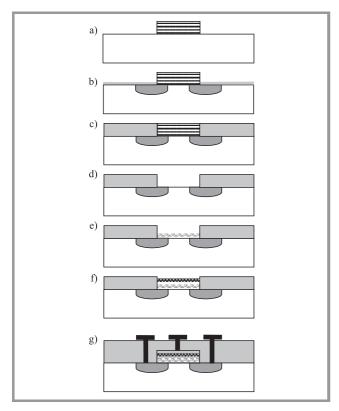

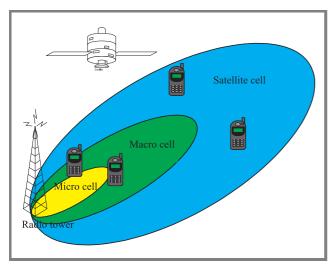

#### 1. Introduction

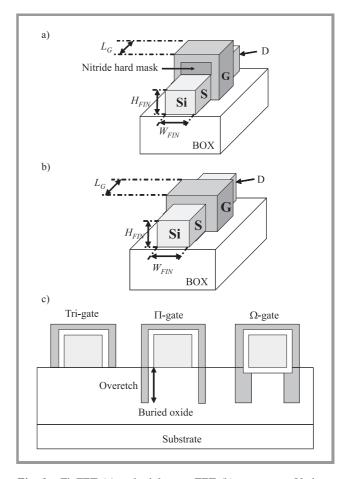

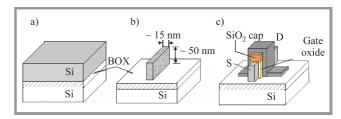

As CMOS is scaled down, the introduction of silicon-oninsulator (SOI) structures is inevitable for improving the short-channel effects, speed, and subthreshold swing. The SOI thickness should be 3-4 times smaller than the channel length and, therefore, stands as a critical parameter for the integration. On the other hand, thin-gate oxides are also necessary for improving the device performance. In this paper, we discuss a number of issues related to the downsizing of planar SOI transistors, focusing on the problems induced by the body thinning and thin gate oxide. A more advanced approach is to use multiple-gate SOI transistors like FinFETs [1] (Fig. 1a), triple-gate FETs [2] (Fig. 1b) or existing variants [3–5] (Fig. 1c). We demonstrate that interesting coupling effects in longitudinal, lateral and vertical directions arise leading to new phenomena. Due to the electrostatic influence of the top and bottom gates, the surface potential and threshold voltage can vary along the lateral gate. Then a bi-dimensional threshold voltage may be observed, depending on the location in the channel. The influence of the back-gate and drain potential, detrimental for single-gate short SOI structures, is also expected to be modified using triple-gate structures because of the threedimensional coupling.

**Fig. 1.** FinFET (a) and triple-gate FET (b) structures. Variants of triple-gate FETs such as Π- and  $\Omega$ -gate FETs (c).

#### 2. Ultra-thin SOI MOSFETs

The SOI film thinning improves the electrostatic control and the device scalability, but also causes special coupling and transport effects.

#### 2.1. Coupling effect

An investigation of the coupling effect between the front and back interfaces (i.e., the front-channel threshold voltage  $V_{T1}$  as a function of the back-gate voltage  $V_{G2}$ , and vice-versa  $V_{T2}(V_{G1})$  [6, 7]) can provide useful information for determining whether one or two channels are created in an SOI film. This is an important point for designing double-gate MOSFETs or FinFETs, since their electrical

2/2007

characteristics are affected by volume inversion [8]. Furthermore, the coupling effect is an essential operation principle for devices in which the threshold voltage is controlled by several gates.

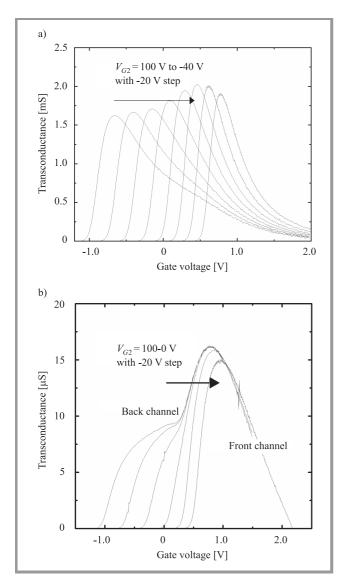

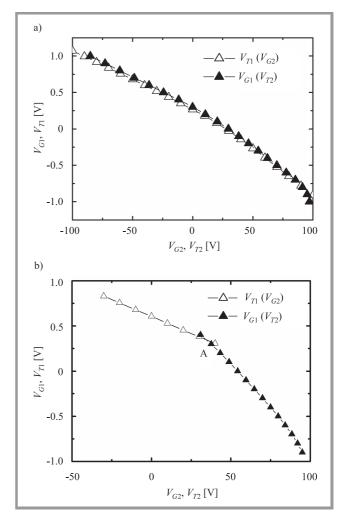

Figures 2a and 2b show the coupling effect between the front and back interfaces in long- and short-channel SOI NMOSFETs. The transconductance curves of a short channel exhibit a single peak (Fig. 2a); however, a plateau appears for a long channel (Fig. 2b) due to the forma-

Fig. 2. Transconductance  $(\delta I_d/\delta V_{G1})$  in SOI NMOSFET versus gate voltage  $V_{G1}$  with the back-gate bias  $V_{G2}$  as a parameter for (a) a short SOI MOSFET ( $L=0.5~\mu{\rm m}$ ) and (b) a long SOI MOSFET ( $L=100~\mu{\rm m}$ ). The plateau due to the back-channel activation is evident for a long transistor. In both cases,  $T_{Si}=15~{\rm nm}$ ,  $T_{BOX}=400~{\rm nm}$ ,  $T_{ox}=2~{\rm nm}$ ,  $W=100~\mu{\rm m}$ , and  $V_D=50~{\rm mV}$ . The doped body ( $N_A\approx 4\cdot 10^{17}~{\rm cm}^{-3}$ ) was thinned by sacrificial oxidation, except in the source/drain regions.

tion of a back inversion layer at the film-BOX interface before the front-channel inversion is created [9]. The back-channel characteristics at various front-gate biases are similar, i.e., the transconductance of a short channel exhibits a single peak [10].

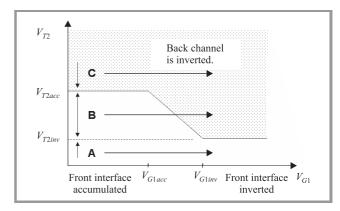

Another interesting feature is that the  $V_{T1}$  ( $V_{G2}$ ) curve is superimposed on the  $V_{G1}$  ( $V_{T2}$ ) one for a short channel (Fig. 3a) while the two curves are different for a long chan-

Fig. 3. (a) Front-channel threshold voltage  $V_{T1}$  versus back gate bias  $V_{G2}$  and back-channel threshold voltage  $V_{T2}$  versus front-gate bias  $V_{G1}$ . Threshold voltages were extracted from the transconductance peak. In a short channel, the two curves are different. (b) In a long channel, the two curves are different. At point A, both the front and back channels are simultaneously inverted.

nel (Fig. 3b). The coupling curves for a long channel are described by [7]:

$$\Delta V_{T1} \approx -\frac{C_{BOX}}{C_{ox}} \Delta V_{G2}, \qquad (1)$$

$$\Delta V_{G1} \approx -\frac{C_{BOX}}{C_{ox}} \frac{C_{si} + C_{ox}}{C_{si}} \Delta V_{T2}, \qquad (2)$$

where  $C_{si} = \varepsilon_{si}/T_{Si}$ ,  $C_{ox} = \varepsilon_{ox}/T_{ox}$ , and  $C_{BOX} = \varepsilon_{ox}/T_{BOX}$  represent the capacitances of the depleted film, gate oxide and buried oxide (BOX), respectively.

The cross-point of these curves (point A in Fig. 3b) indicates the voltage condition at which the front and back

channels are simultaneously inverted [11]. If  $V_{G2}$  is larger than this value, when sweeping  $V_{G1}$ , the back channel is inverted before the front channel. On the other hand, if  $V_{G2}$  is smaller than this value, only the front channel is inverted by sweeping  $V_{G1}$ . Thus, the inverted channel can clearly be identified from point A.

In the case of an extremely thin SOI layer  $(C_{si} >> C_{ox})$ , Eq. (2) can be rewritten as:

$$\Delta V_{G1} \approx -\frac{C_{BOX}}{C_{ox}} \Delta V_{T2} \,. \tag{3}$$

Since the slope of this equation is the same as that of Eq. (1), it is difficult to separate the two curves.

Furthermore, for high series resistance once the back channel is inverted, the formation of the front channel could be masked: the transconductance curve obtained by sweeping  $V_{G1}$  shows a single-peak structure due to the back channel only [10]. Thus, the results in Fig. 2a and Fig. 3a can be

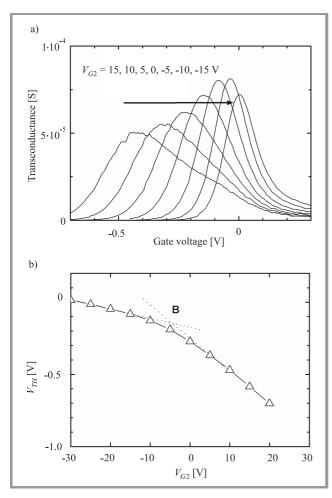

Fig. 4. (a) Transconductance  $(\delta I_D/\delta V_{G1})$  versus front-gate voltage with the back-gate bias as a parameter for the undoped thin-SOI (initial wafer doping was  $N_A=5\cdot 10^{14}~{\rm cm}^{-3}$ ) NMOSFET.  $V_D=10~{\rm mV},\,W=10~{\mu}{\rm m},\,L=0.05~{\mu}{\rm m}.$  The average SOI thickness was 9 nm on the wafer. The gate oxide thickness is approximately 1 nm. (b) Threshold voltage  $V_{th}$  versus back gate voltage  $V_{G2},\,V_D=10~{\rm mV}.$  At point B where the slope changes, both sides are inverted simultaneously.

understood as follows: for a short channel, the back-channel plateau transforms into a peak. When measuring  $V_{T1}(V_{G2})$ , the beginning of the plateau appears as a peak and can be mistaken as  $V_{T1}$ . This peak shows the threshold of the back channel; it actually corresponds to  $V_{G1}(V_{T2})$  as confirmed by our direct back-channel measurements  $V_{T2}(V_{G1})$ . The point where the slope of the curve changes (around  $V_{G2}=20~\mathrm{V}$  in Fig. 3a) corresponds to the voltage condition at which the front and back channels are simultaneously inverted.

As the SOI thickness or channel area decreases, the point where the slope of the coupling curve changes is useful to determine which channel is actually inverted; this identification is impossible from the transconductance curves due to their single-peak shape [12]. Figure 4a reproduces the transconductance curves exhibiting a single peak at various  $V_{G2}$  applied to a short-channel SOI NMOSFET. Figure 4b shows that the threshold voltage is due to the front channel when  $V_{G2}$  is smaller than point B, and to the back channel when  $V_{G2}$  is larger than point B. Note that  $V_{G2}$  at point B is less than 0 V. Hence, the transconductance peak at  $V_{G2} = 0$  V occurs due to the back channel. Transconductance and subthreshold slope deteriorate because the channel is controlled through the gate oxide and silicon body. Thus, this device is not suitable for operation at  $V_{G2} = 0$  V. On the other hand, the transconductance peak reaches a maximum value near the condition where both channels are simultaneously inverted ( $V_{G2} \approx -5$  V in Fig. 4b).

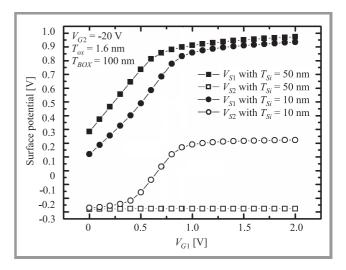

As the SOI thickness decreases below 10 nm, the coupling effect theory should be revisited [13]. Figure 5 shows

*Fig. 5.* Surface potential of the front  $(V_{S1})$  and back  $(V_{S2})$  interfaces versus front-gate voltage  $(V_{G1})$  in the case of thick (50 nm) and thin (10 nm) SOI. Back gate voltage  $V_{G2} = -20$  V.

the simulated results of the surface potential variation with the front-gate voltage for a negative back-gate bias. In a thick-body MOSFET, as  $V_{G1}$  increases, the front channel is gradually inverted whereas the back-surface potential does not change, remaining in accumulation. By contrast,

in an ultra-thin body, both the front and back potentials increase with  $V_{G1}$ . This means that it becomes difficult to keep one channel in accumulation while inverting the opposite channel. Additional simulations show that the potential distribution in a 5 nm thick body is quasi-flat. The two channels merge in a single channel that covers the whole film volume [13]. Ultra-thin SOI devices are also subject to quantum effects: sub-band splitting which leads to an increase in the threshold voltage and a modification of the effective mass and scattering mechanisms.

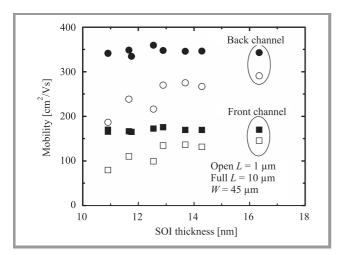

#### 2.2. Carrier mobility

The effect of the film thickness on mobility is important for further CMOS performance and scalability. Figure 6 shows the mobility-thickness correlation in 10–20 nm thick NMOSFETs with a 2-nm SiO<sub>2</sub> gate oxide, in which SOI thickness variations were locally caused by process fluctuations. In short-channel MOSFETs, the mobility decreases for thinner films, whereas in long MOSFETs the thickness effect is insignificant. This difference is essentially due to the series resistance. This argument applies to both the front and back channels [14].

*Fig. 6.* Front- and back-channel field-effect mobilities versus SOI film thickness for short (1 μm) and long (10 μm) channels. The field-effect mobility was determined from the transconductance peak. All the devices were probed on the same wafer. The local film thickness was measured by ellipsometry and verified by analyzing the coupling between the front and back channels.  $T_{ox} = 2$  nm and  $T_{BOX} = 400$  nm. The doped body ( $N_A \approx 4 \cdot 10^{17}$  cm<sup>-3</sup>) was thinned by sacrificial oxidation, except in the source/drain regions.

The mobility is systematically lower at the front channel than at the back channel, even after correcting for a lowered gate-oxide capacitance due to polysilicon depletion and quantum capacitance of the inversion layer. Comparing the effective mobility at the front and back channels makes the origin of the mobility difference clear.

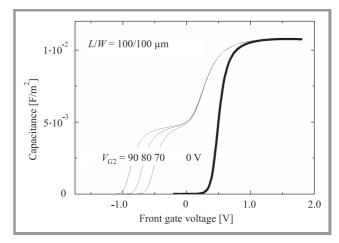

The front-gate split C-V method was used for determining the carrier mobility and density,  $N_s$ , at both the front and back channels. As shown in Fig. 7, a plateau is observed in

*Fig.* 7. Front-gate split C-V measurements for various substrate voltages.  $T_{Si} \approx 16$  nm. The frequency for split C-V measurement is 5 kHz.

the C-V plot at large substrate voltages due to the creation of the back channel [15]. The carrier density  $N_s$  of the back channel can be obtained by integrating the capacitance values specific to this region [16, 17]:

$$qN_{s Back}(V_{G1}, V_{G2}) = \int_{-\infty}^{V_{G1}} C_{gc} \, dV_{G1}.$$

(4)

The effective field is determined from the equations for thin SOI [18, 19]. The threshold voltage is calculated by defining a corresponding inversion charge density [17]. There is, however, a limitation in this front-gate split C-V method for evaluating the carrier density in the back channel [17]. Figure 8 shows the relationship between the back-channel threshold voltage  $V_{T2}$  and front-gate volt-

Fig. 8. The relationship between the threshold voltage of the back channel  $(V_{T2})$  and the front-gate voltage  $(V_{G1})$  by the model of Lim and Fossum. When the front interface is accumulated  $(V_{T1acc})$ , the threshold voltage of the back channel becomes constant. When the back gate is in region A and the front gate is swept, only the front channel is inverted. When the back gate is in region B and the front gate is swept, the back channel is turned off and on by the front gate voltage. When the back gate is in region C and the front gate is swept, the back channel cannot be turned off by the front gate voltage because of the accumulation layer at the front interface.

age  $V_{G1}$  as modeled by Lim and Fossum [7]. For the back gate bias in region A, only the front channel is activated by applying the front-gate voltage. Thus, the carrier density at the front channel can be evaluated by the front-gate split C-V method. For the back gate bias in region B, the back channel can be turned on and off by sweeping the frontgate voltage. Thus, the carrier density at the back channel can be evaluated by the front-gate split C-V method. On the other hand, for the back gate bias in region C, when  $V_{G1}$  is swept, it is impossible to cut off the back channel since  $V_{T2}$  becomes constant when the front interface is accumulated. Furthermore, in this region C, a careful examination is required for getting the correct C-V curves. The front-interface accumulation layer is not formed instantly as there is no source for the majority carrier in SOI films. A hysteresis in C-V and I-V is therefore observed [15, 20]. Thus, the front-gate split C-V method cannot be used for determining the carrier density at the back channel in region C.

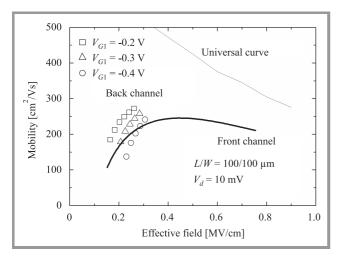

*Fig. 9.* Front-channel effective mobility (for  $V_{G2} = 0$  V) and back-channel effective mobility (for  $V_{G1} = -0.2, -0.3$ , and -0.4 V) versus effective field.

Figure 9 shows the effective mobility of the front  $(\mu_{eff,F})$  and back  $(\mu_{eff,B})$  channels evaluated by  $I_D - V_G$  and front-gate split C-V method for our devices of Fig. 6. For low  $|V_{G1}|$ ,  $\mu_{eff,B}$  is clearly higher than  $\mu_{eff,F}$  at the same effective field  $E_{eff}$ . The mobility components  $\mu_{Fl}$  and  $\mu_{Bl}$  which indicate the deviation from the "universal mobility" curve were estimated by Matthiessen's rule:

$$\mu_{Fl,Bl}^{-1}(N_s) = \mu_{effF,effB}^{-1}(N_s(E_{eff})) - \mu_{universal}^{-1}(E_{eff}).$$

(5)

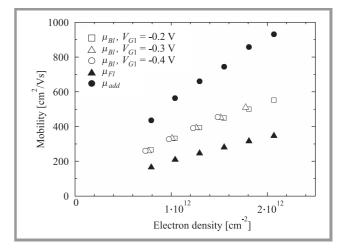

This procedure removes the impact of phonon scattering. Figure 10 shows that these mobility components depend on  $N_s$ , which suggests the role of Coulomb scattering.  $V_{G1}$  dependence of  $\mu_{eff,B}$  in Fig. 9 is explained by the change in  $N_s$ . At a constant  $E_{eff}$ ,  $N_s$  decreases with a more negative  $V_{G1}$ , which results in a reduced charge-screening effect.

Furthermore, since  $\mu_{Fl} < \mu_{Bl}$ , an additional scattering mechanism would affect only the front channel.

We extract  $\mu_{add}$  on the basis of the mobility difference between the two channels as follows:

$$\mu_{add}^{-1}(N_s) = \mu_{Fl}^{-1}(N_s) - \mu_{Bl}^{-1}(N_s). \tag{6}$$

Note that the mobility limited by Coulomb scattering on film impurities is now eliminated. The dependence of  $\mu_{add}$  on  $N_s$  (Fig. 10) suggests that the presence of Coulomb scat-

*Fig. 10.* Mobility-lowering components of the front channel  $\mu_{Fl}$  and back channel  $\mu_{Bl}$  determined from Eq. (5). The additional mobility-lowering component  $\mu_{add}$  of the front channel was derived from Eq. (6).

tering centers at the front channel is responsible for the mobility difference between the two channels. Remote scattering centers from the polysilicon gate are possible candidates and should be considered for thin-gate oxides [21].

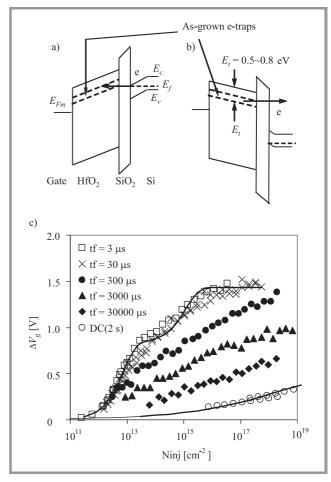

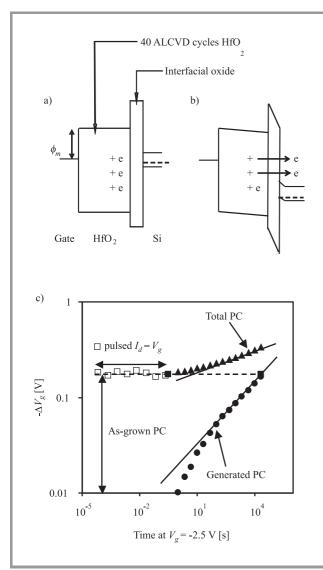

#### 2.3. Thin gate oxide

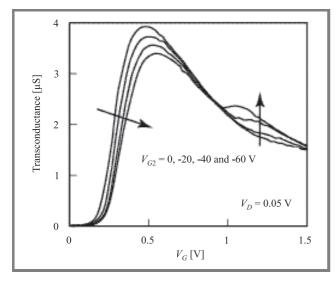

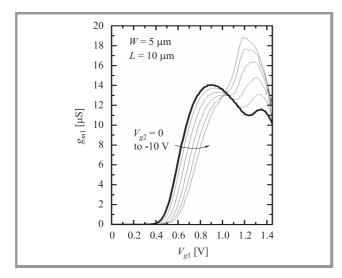

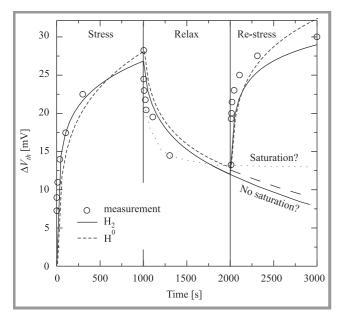

An important effect in SOI MOSFETs with ultra-thin oxides is the gate-induced floating-body effect (GIFBE) [22]. This effect is caused by the tunneling current from the valence band of the SOI film into the gate [23], which charges the body with majority carriers. The body potential is determined by the balance between the body charging via direct tunneling current and the carrier recombination in the body or junctions. Due to the GIFBE, the transconductance curve becomes distorted giving rise to a second peak, as shown in Fig. 11.

The GIFBE occurs even in FD MOSFETs, especially when the back interface is biased close to accumulation [24]. The standard method to determine the mobility in FD SOI MOSFETs consists of eliminating the interface coupling by accumulating the opposite channel. Figure 11 shows that the second peak of transconductance due to the GIFBE becomes larger than the genuine peak. If the "maximum" transconductance is misused, then the field-effect mobility is overestimated.

2/2007

*Fig. 11.* Transconductance as a function of the front gate voltage for different back-gate biases from 0 V to -10 V in a FD SOI MOSFET.  $T_{BOX} = 145$  nm,  $T_{ox} = 1.6$  nm, and  $T_{Si} = 17$  nm. The "second peak" appears due to the GIFBE.

## 3. Non-planar multiple-gate SOI transistors

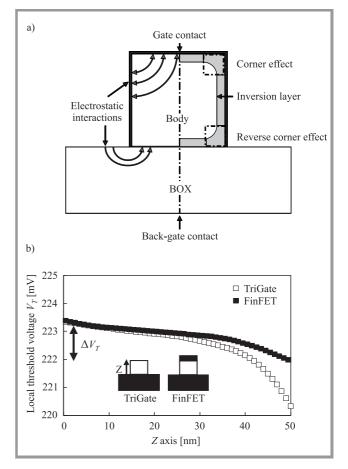

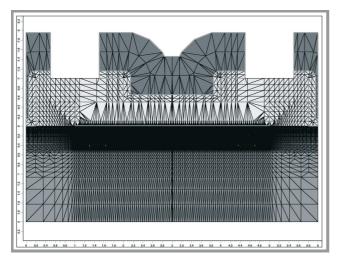

#### 3.1. Corner effects

Triple-gate devices feature a non planar silicon/oxide interface involving corners (Fig. 1b). In each corner region (Fig. 12a), the coupling between the adjacent gates induces a local lowering of the threshold voltage. This parasitic channel may cause an increase of the off-state leakage current. In order to characterize the threshold voltage inhomogeneity, we performed numerical simulations. The "local" threshold voltage of the different channel regions was extracted from the electrical characteristics. First, the "global" threshold voltage  $V_{TG}$  was determined from the second derivative of the drain current versus gate voltage curve. Then, the electron density for  $V_G = V_{TG}$  was calculated all along the channel. Finally, using the relationship between the threshold voltage and the inversion charge, a "local" threshold voltage was calculated:

$$V_T^{LOCAL} = V_{TG} - \frac{Q_{INV}}{C_{OX}}.$$

(7)

The local threshold voltage along the vertical channel for undoped FinFET and triple-gate (TriGate) transistors is plotted in Fig. 12b. The threshold of a triple-gate structure is found to decrease near the top gate. For FinFETs, the deactivation of the top channel by the nitride hard mask suppresses the drop of the threshold voltage and the profile is roughly flat along the channel.

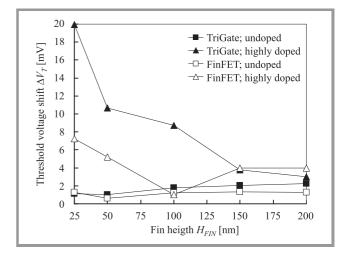

The  $\Delta V_T$  is defined as the maximum threshold lowering along the vertical axis. In Fig. 13,  $\Delta V_T$  is plotted as a function of the fin height for FinFETs and triple-gate FETs, with low and high doping. As expected, tall fins

*Fig. 12.* (a) Cross-section of a triple-gate structure showing the electrostatic interactions leading to corner effects. (b) Local threshold voltage along the vertical channel for low doped  $(N_A=10^{15}~{\rm cm}^{-3})$  FinFET and triple-gate FET with  $W_{FIN}=50~{\rm nm}$ ,  $H_{FIN}=50~{\rm nm}$ , and  $L_G=0.5~{\rm μm}$ .

*Fig. 13.*  $\Delta V_T$  versus fin height  $H_{FIN}$  for FinFET and triple-gate structures with low ( $N_A = 10^{15} \text{ cm}^{-3}$ ) and high ( $N_A = 10^{18} \text{ cm}^{-3}$ ) body doping.  $W_{FIN} = 50 \text{ nm}$ ,  $L_G = 500 \text{ nm}$ .

exhibit a lower  $\Delta V_T$  because of a smaller top-gate influence. In FinFETs the threshold voltage shift is efficiently reduced due to their quasi-double gate operation. A low

doping clearly attenuates the threshold voltage shift for both FinFET and triple-gate architectures. Although the threshold voltage non-uniformity increases with the doping level,  $\Delta V_T$  shift due to the non-planar triple-gate configuration is smaller than 25 mV, indicating a weak impact of the corners

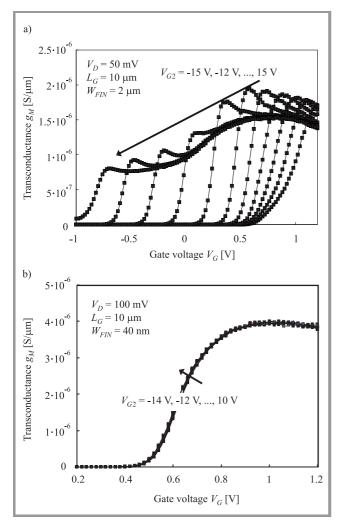

#### 3.2. Lateral versus vertical coupling

The  $\Omega$ FETs are triple-gate transistors where the lateral gates penetrate within the BOX (Fig. 1c) [5]. A wide  $\Omega$ FET behaves as a single-gate fully depleted (FD SOI) device rather than a FinFET. Changing the back-gate bias  $V_{G2}$  from -15 to +15 V results in a lateral shift of the current and transconductance characteristics (Fig. 14a). The back-channel activation is visible on transconductance curves as a plateau (for  $V_{G2}=+15$  V and  $V_{G}=-0.5$  V, see also Fig. 2b).

*Fig. 14.* (a) Transconductance  $g_M$  versus gate voltage  $V_G$  for a wide  $(W_{FIN}=2~\mu \mathrm{m})~\Omega \mathrm{FET}$ . The back-gate voltage  $V_{G2}$  varies from -15 to  $15~\mathrm{V}$ . (b) Transconductance  $g_M$  versus gate voltage  $V_G$  for a narrow  $(W_{FIN}=40~\mathrm{nm})~\Omega \mathrm{FET}$ . The back-gate voltage  $V_{G2}$  varies from -14 to  $10~\mathrm{V}$ .

For narrow devices (Fig. 14b), the substrate bias is no longer effective. The silicon-BOX interface becomes controlled by the fringing electric field penetrating from the lateral gates into the channel (horizontal coupling) and into the BOX. For instance, when the front gate is in accumulation, it is impossible to invert the back channel even for high back-gate bias.

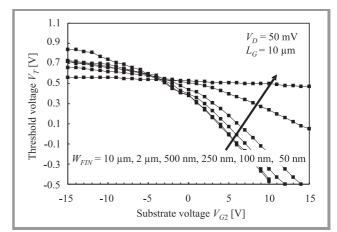

The threshold voltage variation with substrate bias is shown in Fig. 15. For *wide* devices, the change from substrate ac-

*Fig. 15.* Threshold voltage  $V_T$  versus back-gate bias  $V_{G2}$  for n-channel ΩFETs with various fin widths.  $V_T$  was extracted using a constant current method.

cumulation to substrate inversion is reflected by a linear decrease of the threshold voltage, followed by a more rapid drop due to the activation of the back channel (1D Lim and Fossum model, see also Fig. 3 [7]). As noted above, the lateral gates can screen the narrow silicon body from the back-gate influence. In Fig. 15, it is seen that for devices with very small fin width the threshold voltage is rather insensitive to back-gate voltage. In  $\Omega$ FET devices, the control of the body and back channel by the main gate is better than in FinFETs.

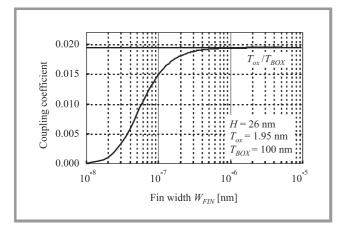

The potential distribution in the channel of a triple-gate structure can be analytically calculated by adapting the model proposed for four-gate FETs [25]. The variation of the threshold voltage when the back-gate is biased into depletion (vertical coupling: Eq. (1)) can then be rewritten to take into account the influence of the lateral coupling:

$$\alpha(W, H) = \frac{\partial V_{T1}}{\partial V_{G2}}$$

$$= \left[ \frac{2\sqrt{2}}{\sinh\left(2\sqrt{2}\frac{H}{W}\right)} \right] \frac{\frac{C_W(W)}{C_{ox}}}{1 + \frac{2\sqrt{2}}{\tanh\left(2\sqrt{2}\frac{H}{W}\right)} \frac{C_W(W)}{C_{BOX}}},$$

(8)

where  $C_W = \varepsilon_{Si}/W_{FIN}$ ,  $C_{ox}$  and  $C_{BOX}$  are respectively the lateral silicon film capacitance, front and back oxide capacitances.

In Fig. 16, the 2D coupling coefficient  $\alpha$ , which generalizes Fossum's model [7], is plotted as a function of the channel width. For a narrow triple-gate the coefficient is close to zero; this corresponds to the situation where the lateral gates control perfectly the body, screening the influence of the back-gate. For a fully depleted SOI configuration, i.e., W >> H, the coupling coefficient  $\alpha$  is close to the classical value  $T_{ox}/T_{BOX}$ , given in Eq. (1).

*Fig. 16.* Coupling coefficient  $\Delta V_{T1}/\Delta V_{G2}$  (back-gate biased into depletion) as a function of the fin width in a triple-gate transistor.

Practical implications of back-gate coupling in multiple-gate FETs are related to resistance to harsh environment with radiation or hot carrier injection, where charges trapped into the BOX can modify the electrostatic potential of the back interface. Radiation tests on  $\Omega$ FET devices [26] have shown that wide devices exhibit a 200 mV threshold voltage shift after 500 krad exposure. By contrast, narrow devices (50 nm) experience a quasi-null threshold voltage variation. Narrow  $\Omega$ FETs are therefore intrinsically immune to radiation effects and could operate in very harsh conditions.

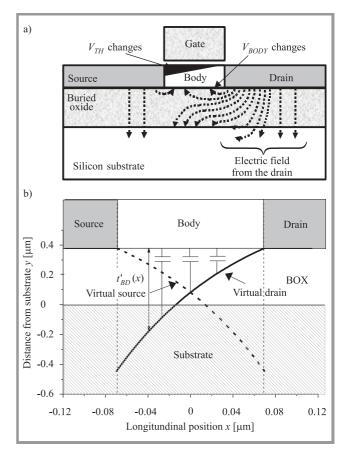

#### 3.3. Lateral versus longitudinal coupling - DIVSB

A dramatic short-channel effect in fully depleted SOI structures is the penetration of the electric field from the drain into the buried oxide and underlying silicon substrate (Fig. 17a). This fringing field tends to increase the surface potential at the back interface (film-BOX). Because of the existing vertical coupling between the front and back interfaces, the properties of the front channel are degraded.

The potential profile in the buried oxide can be resolved by conformal mapping [27]. Deriving the potential at the body/BOX interface, the expressions of the back-channel transverse field components can be calculated. The source/body  $C_{BS}(x)$  and drain/body  $C_{BD}(x)$  capacitances

*Fig. 17.* (a) Schematics of the fringing fields leading to DIVSB effect and (b) equivalent representation of buried oxide fringing capacitances and source/drain virtual electrodes.

summarize the back-channel charge control by the source and drain:

$$C_{BS/BD}(x) = \frac{\varepsilon_{ox}}{T_{BOX}} \frac{1}{\exp\left[\frac{\pm \pi}{T_{BOX}} \left(x \pm \frac{L}{2}\right)\right] - 1}.$$

(9)

A very interesting feature of this formalism is the fact that the fringe capacitances  $C_{BD}$  and  $C_{BS}$  behave like the BOX capacitance  $C_{BOX}$ . This means that drain and source influence can be described by *virtual* electrodes located at a varying distance from the body/BOX interface (Fig. 17b). This is why the phenomenon is named DIVSB (drain induced virtual substrate biasing) [27].

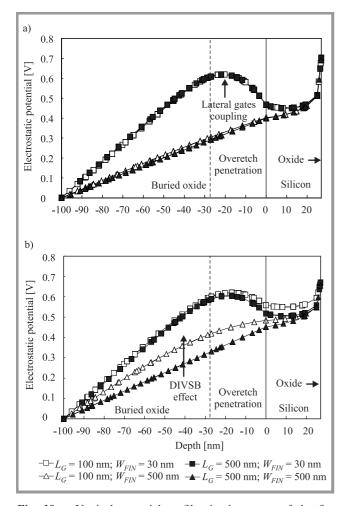

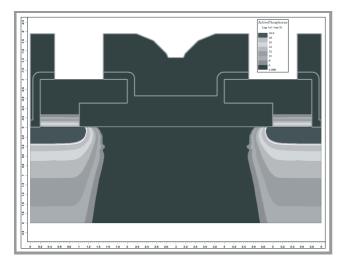

The 3D simulations were carried out to investigate the evolution of DIVSB effect as a function of fin width. The vertical potential profiles taken in the centre of the device (at  $L_G/2$  and  $W_{FIN}/2$ ) are presented in Fig. 18. At low drain voltage (10 mV, Fig. 18a) the potential depends exclusively on the fin width. For narrow  $\Omega$ FETs, the BOX region located between the two lateral gates is totally under control and the potential exhibits a peak. For wide devices, the lateral gates have no influence. For high drain voltage (1.2 V, Fig. 18b) DIVSB effect is directly visible in a short and wide device, where the potential in the BOX is increasing as compared to a long and wide device. This

Fig. 18. Vertical potential profiles in the centre of the fin. Simulations are for short (open symbols) and long (closed symbols), as well as for narrow (squares) and wide (triangles) devices; (a) is simulated with a low drain voltage ( $V_D = 10 \text{ mV}$ ) and (b) with a high drain voltage ( $V_D = 1.2 \text{ V}$ );  $V_G - V_T = 300 \text{ mV}$ , and  $V_{G2} = 0 \text{ V}$ .

critical problem is solved for narrow fins, where the potential profile in the BOX is roughly the same for long and short devices.

#### 4. Summary

Several dimensional effects taking place in modern SOI MOSFETs have been reviewed. In planar transistors, the film thickness plays a crucial role. The coupling effects are amplified in ultra-thin films preventing the separation between the front and back channels. The coexistence of accumulation in the back channel with inversion in the front channel becomes equally difficult. In addition, the high series resistance caused by film thinning can mask the activation of one channel. The method for determining the inverted channel was described.

The carrier mobility in ultra-thin SOI MOSFETs can be extracted by adapting the front-gate split C-V method to the back channel. It was found that the mobility in the front

channel is smaller than that in the back channel due to Coulomb scattering. The possibility of misevaluation of the carrier mobility, due to direct tunneling from the valence band through very thin gate oxides and related floating-body effects, was pointed out.

In non-planar FinFET-like transistors, additional size and coupling effects are induced by the multiple gates. We showed that the corner effect, i.e., the influence of a gate on the threshold voltage of an adjacent gate, is very small when using low-doped bodies or tall fins. The back-gate influence, which can modify the threshold voltage of the device and activate a back-channel, is screened for narrow fins by the strong coupling between the lateral gates. The drain-to-BOX coupling and the radiation effects are also reduced in narrow devices by the interaction of the lateral gates.

This paper addressed a number of SOI mechanisms that require further modeling, characterization and control. However, the use of SOI technology is not debatable. SOI is the necessary solution for extending the miniaturization of CMOS circuits.

#### Acknowledgements

We would like to thank our colleagues who have contributed to this work: J. Pretet, S. Eminente, M. Cassé, A. Vandooren, X. Mescot, F. Daugé, T. Poiroux, K. Akarvardar, T. Ernst, and A. Zaslavsky.

#### References

- D. Hisamoto et al., "A folded-channel MOSFET for deep-sub-tenth micron era", in *IEDM'98 Tech. Dig.*, San Francisco, USA, 1998, pp. 1032–1034.

- [2] B. Doyle et al., "Tri-gate fully-depleted CMOS transistors: fabrication, design and layout", in VLSI 2003 Tech. Dig., Washington, USA, 2003, pp. 132–133.

- [3] J.-T. Park, J.-P. Colinge, and C. H. Diaz, "Pi-gate SOI MOSFET", IEEE Electron Dev. Lett., vol. 22, no. 5, pp. 405–406, 2001.

- [4] F.-L. Yang et al., "25 nm CMOS omega FETs", in IEDM'02 Tech. Dig., San Francisco, USA, 2002, pp. 255–258.

- [5] C. Jahan et al., "10 nm ΩFETs transistors with TiN metal gate and HfO<sub>2</sub>", in VLSI 2005 Tech. Dig., Kyoto, Japan, 2005, pp. 112–113.

- [6] S. Cristoloveanu and S. S. Li, Electrical Characterization of SOI Materials and Devices. Boston: Kluwer, 1995.

- [7] H. K. Lim and J. G. Fossum, "Threshold voltage of thin-film siliconon-insulator (SOI) MOSFET's", *IEEE Trans. Electron Dev.*, vol. 30, no. 10, pp. 1244–1251, 1983.

- [8] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-gate silicon on insulator transistor with volume inversion: a new device with greatly enhanced performance", *IEEE Electron Dev. Lett.*, vol. 8, no. 9, pp. 410–412, 1987.

- [9] T. Ouisse, S. Cristoloveanu, and G. Borel, "Influence of series resistances and interface coupling on the transconductance of fully-depleted silicon-on-insulator MOSFETs", *Solid-State Electron.*, vol. 35, no. 2, pp. 142–149, 1992.

- [10] A. Ohata, S. Cristoloveanu, M. Cassé, A. Vandooren, and F. Daugé, "Coupling effect between the front and back interfaces in thin SOI MOSFETs", *Microelectron. Eng.*, vol. 80, no. 17, pp. 245–248, 2005.

2/2007

- [11] A. Ohata, J. Pretet, S. Cristoloveanu, and A. Zaslavsky, "Correct biasing rules for virtual DG mode operation in SOI-MOSFETs", *IEEE Trans. Electron Dev.*, vol. 52, no. 1, pp. 124–125, 2005.

- [12] A. Ohata, S. Cristoloveanu, M. Cassé, A. Vandooren, and F. Daugé, "Characterization of ultra-thin SOI MOSFETs by coupling effect between front and back interfaces", in *IEEE Int. SOI Conf.*, Hawaii, USA, 2005, pp. 63–64.

- [13] S. Eminente, S. Cristoloveanu, R. Clerc, A. Ohata, and G. Ghibaudo, "Ultra-thin fully-depleted SOI MOSFETs: special charge properties and coupling effect", *Solid-State Electron.*, vol. 51, no. 2, pp. 239–244, 2007.

- [14] A. Ohata, S. Cristoloveanu, and M. Cassé, "Mobility comparison between front and back channels by front-gate split capacitancevoltage method", *Appl. Phys. Lett.*, vol. 89, no. 3, p. 032104, 2006.

- [15] J. Chen, R. Solomon, T. Y. Chan, K. P. Ko, and C. Hu, "Threshold voltage and CV characteristics of SiO<sub>2</sub> MOSFET's related to Si film thickness variations on SIMOX wafers", *IEEE Trans. Electron Dev.*, vol. 39, no. 10, pp. 2346–2353, 1992.

- [16] D. Esseni, M. Mastrapasqua, G. K. Celler, C. Fiegna, L. Selmi, and E. Sangiorgi, "Low field electron and hole mobility of SOI transistors fabricated on ultrathin silicon films for deep submicrometer technology application", *IEEE Trans. Electron Dev.*, vol. 48, no. 12, pp. 2842–2850, 2001.

- [17] A. Ohata, M. Cassé, and S. Cristoloveanu, "Front and back channel mobility in ultrathin SOI-MOSFETs by front-gate split CV method", Solid-State Electron., vol. 51, no. 2, pp. 245–251, 2007.

- [18] M. J. Sherony, L. T. Su, J. E. Chung, and D. A. Antoniadis, "SOI MOSFET effective channel mobility", *IEEE Trans. Electron Dev.*, vol. 41, no. 2, pp. 276–278, 1994.

- [19] J. Choi, Y. Park, and H. Min, "Electron mobility behavior in extremely thin SOI MOSFET's", *IEEE Electron Dev. Lett.*, vol. 16, no. 11, pp. 527–529, 1995.

- [20] M. Bawedin, S. Cristoloveanu, J. G. Yun, and D. Flandre, "A new memory effect (MSD) in fully depleted SOI MOSFETs", *Solid-State Electron.*, vol. 49, no. 9, pp. 1547–1555, 2005.

- [21] M. S. Krishnan, Y. Yeo, Q. Lu, T. King, J. Bokor, and C. Hu, "Remote charge scattering in MOSFETs with ultra-thin gate dielectrics", in *IEDM'98 Tech. Dig.*, San Francisco, USA, 1998, pp. 571–573.

- [22] J. Pretet, T. Matsumoto, T. Poiroux, S. Cristoloveanu, R. Gwoziecki, C. Raynaud, A. Roveda, and H. Brut, "New mechanism of body charging in partially depleted SOI-MOSFETs with ultra-thin gate oxides", in *Proc. 32th Eur. Solid-State Dev. Res. Conf. ESSDERC'02*, Firenze, Italy, 2002, pp. 515–518.

- [23] A. Modelli, "Valence band electron tunneling in metal-oxide-siliconstructures", Appl. Surf. Sci., vol. 30, pp. 298–303, 1987.

- [24] M. Cassé, J. Pretet, S. Cristoloveanu, T. Poiroux, C. Fenouillet-Beranger, F. Fruleux, C. Raynaud, and G. Reimbold, "Gate-induced floating-body effect in fully-depleted SOI MOSFETs with tunneling oxide and back gate biasing", *Solid-State Electron.*, vol. 48, no. 7, pp. 1243–1247, 2004.

- [25] K. Akarvardar, S. Cristoloveanu, and P. Gentil, "Threshold voltage model of the SOI 4-gate transistor", in *IEEE Int. SOI Conf.*, Charleston, USA, 2004, pp. 89–90.

- [26] M. Gaillardin, P. Paillet, V. Ferlet-Cavrois, S. Cristoloveanu, O. Faynot, and C. Jahan, "High tolerance to total ionizing dose of Ω-shaped gate field-effect transistors", *Appl. Phys. Lett.*, vol. 88, p. 223511, 2006.

- [27] T. Ernst and S. Cristoloveanu, "Buried oxide fringing capacitance: a new physical model and its implication on SOI device scaling and architecture", *IEEE Int. SOI Conf.*, Rohnert Park, USA, 1999, pp. 38–39.

University and IMEP. e-mail: ohata@enserg.fr IMEP Minatec-INPG 3 Parvis Louis Néel Grenoble BP257, France

Akiko Ohata received the M.Sc. degree in theoretical physics and Ph.D. degree in electronics from Tokyo Institute of Technology, Japan. She has engaged in research of Si quantum devices, single electron devices and SOI MOSFETs in Toshiba Corporation, RIKEN Institute, Tokyo Institute of Technology, Gunma

Romain Ritzenthaler was born in Rouen, France, in 1980. He received the M.Sc. degree from the Ecole Nationale Superieure de Physique de Grenoble (ENSPG) in 2003, Grenoble, France. He is currently pursuing his Ph.D. degree with the CEA-Laboratoire d'Electronique et Technologie de l'Information (LETI), Greno-

ble, France. His work is dedicated to the realization, characterization and simulation of the FinFET devices.

e-mail: ritz\_romain@hotmail.com

IMEP Minatec-INPG 3 Parvis Louis Néel Grenoble BP257, France

CEA-LETI

17 avenue des Martyrs

38054 Grenoble cedex 9, France

Sorin Cristoloveanu received the Ph.D. (1976) and the French Doctorat ès-Sciences (1981) from the National Polytechnic Institute, Grenoble, France. He joined the Centre National de la Recherche Scientifique (CNRS) and became a Director of Research in 1989. He worked at JPL (Pasadena) and at the Universities of Maryland,

Florida (Gainesville) and Nashville. He served as Director of the LPCS Laboratory and of the Center for Advanced Projects in Microelectronics (CPMA Grenoble). He is the author or co-author of more than 600 technical journal papers and conference presentations (including 80 invited contributions). He authored or edited 15 books, and

organized 14 international conferences. He is a Fellow of IEEE, a Fellow of the Electrochemical Society, and Editor of "Solid-State Electronics".

e-mail: sorin@enserg.fr IMEP Minatec-INPG 3 Parvis Louis Néel Grenoble BP257, France

Olivier Faynot received the M.Sc and Ph.D. degrees from the Institut National Polytechnique de Grenoble, France, in 1991 and 1995, respectively. His doctoral research was related to the characterization and modeling of deep submicron fully depleted SOI devices fabricated on ultra-thin SIMOX wafers. He joined LETI

(CEA-Grenoble, France) in 1995, working on simulation and modeling of deep submicron fully and partially depleted SOI devices. His main activity was the development of a dedicated partially depleted SOI model, called LETI SOI. From 2000 to 2002, he was involved in the development of a sub 0.1  $\mu$ m partially depleted technology. Since 2003, he is in charge of the development of advanced single and multiple-gate fully depleted SOI technologies with high k and metal gate. He is author and co-author of more than 70 scientific publications on SOI in journals and international conferences. From 2001 to 2003, Doctor Faynot was on the IEEE International SOI Conference Committee. In 2002 and 2003, he was in the International Electron Device Meeting (IEDM) technical committee. Since 2004, Doctor Faynot joined the Solid State Device and Materials (SSDM) Conference Committee.

e-mail: ofaynot@cea.fr CEA-LETI 17 avenue des Martyrs 38054 Grenoble cedex 9, France Invited paper

# Challenges for 10 nm MOSFET process integration

Mikael Östling, Bengt Gunnar Malm, Martin von Haartman, Julius Hållstedt, Zhen Zhang, Per-Erik Hellström, and Shili Zhang

Abstract—An overview of critical integration issues for future generation MOSFETs towards 10 nm gate length is presented. Novel materials and innovative structures are discussed. The need for high-k gate dielectrics and a metal gate electrode is discussed. Different techniques for strain-enhanced mobility are discussed. As an example, ultra thin body SOI devices with high mobility SiGe channels are demonstrated.

Keywords—sstrained silicon, silicon germanium, silicon-oninsulator (SOI), high-k dielectrics, hafnium oxide, nano-wire, low-frequency noise, mobility, metal gate.

#### 1. Introduction

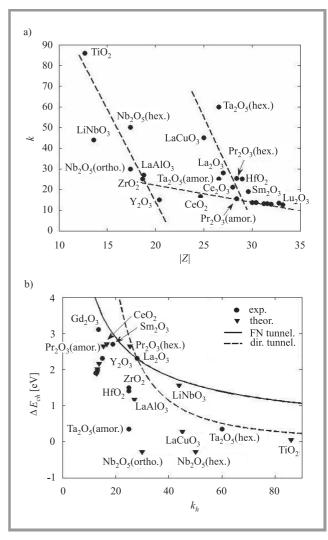

The International Technology Roadmaps for Semiconductors (ITRS) [1] identifies a number of challenges for continued successful scaling of MOSFET technology. It is clear that new materials and process modules will be needed to meet the ITRS roadmap requirements and enhance performance for a given technology node. In this review we focus on the challenges for the 45 nm node and beyond. Although some of the discussed topics, e.g., strain-enhanced mobility, were introduced already at the 90 nm node their importance will certainly continue to increase. The main integration issues, which will be presented here, are:

- Replacing the standard SiO<sub>2</sub> gate oxide or oxynitride by a high-k/metal gate stack. This transition is required at an equivalent oxide thickness of about 1.2 nm, which has already been used in volume production from the 90 nm node.

- Strain-enhanced mobility. Process induced stress is now widely used to improve the performance of both n- and p-channel MOSFETs. Uniaxial stress, induced locally in the channel region, is the preferred integration method, while different types of strainengineered substrates, usually with biaxial strain, are also very promising candidates.

- As the channel length is scaled down, leading to increased current density, the parasitic resistances in the extension and source/drain regions must be minimized. The ITRS roadmap clearly indicates that the main obstacle for the ultimate scaling towards 10 nm is the source/drain and contact resistance, which cannot be reduced enough in relation to the increasing current densities in sub 50 nm multi-gate devices [2]. A possible solution to this, is the use of complementary Schottky contacts to PMOS and NMOS, respectively [3].

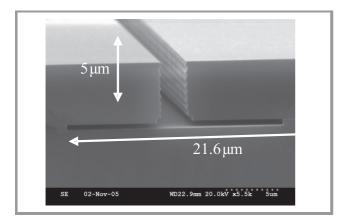

Other integration issues include the choice of structureplanar or multigate and substrate type bulk, SOI or even strained virtual substrates. Conventional planar CMOS on bulk substrates has a significant limitation due to poor control of short channels effects (SCE). A promising alternative is ultra-thin body (UTB) SOI MOSFETs with lowly doped channels, which also offer higher mobility in addition to reduced SCE and junction leakage. Using double or multiple gates improves the electrostatic control of the channel. Of the different types of multi gate devices the FinFET [4] has received the most attention. A comprehensive analysis of FinFET structures showed that the double gate structure is preferred over more advanced triple gate or gate-all around structures [5]. One of the key metrics is the effective channel width, which can be achieved for a given layout area. The channel width is traded off against sub-threshold slope or other indicators of degraded short SCE. An innovative device structure, featuring an inverted-T channel, was recently demonstrated [6]. This device combines the thin body SOI and the FinFET structures to achieve better on-current to area ratio. For the ultimate CMOS, silicon nanowires are promising, thanks to the optimized SCE control, using a gate-all-around structure [7].

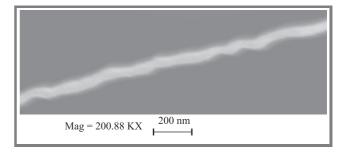

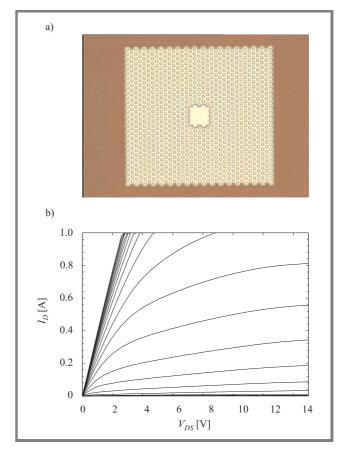

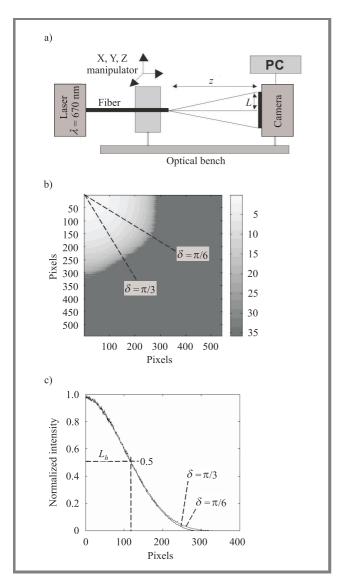

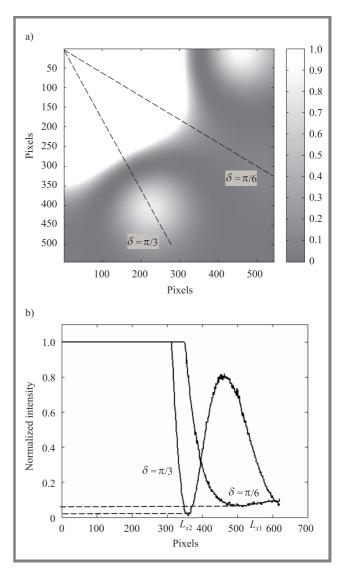

Optical lithography of 10 nm gate lines will be a serious challenge, due to effects such as line edge roughness (LER) and line width roughness (LWR). If electron beam lithography is used lateral straggle gives rise to similar issues. As we approach the 10 nm node length good control of the effective channel length must be maintained to minimize short channel effects and fluctuations in, e.g., threshold voltage. An illustration of LER is given in Fig. 1,

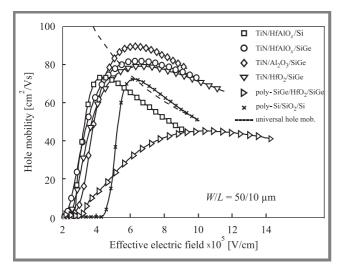

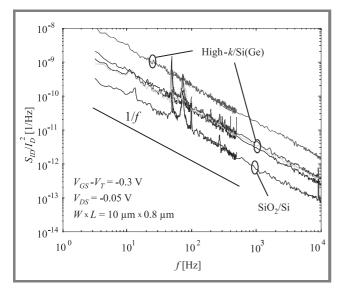

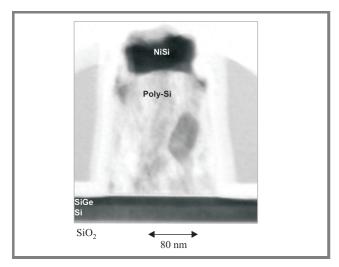

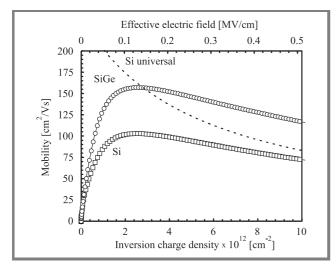

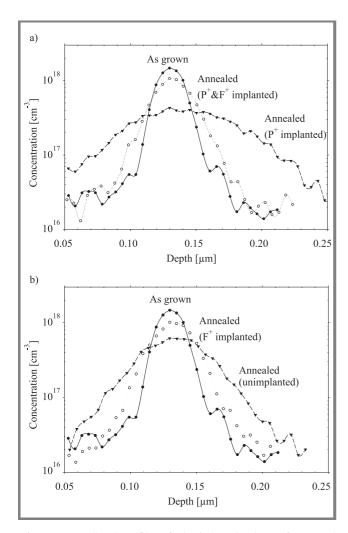

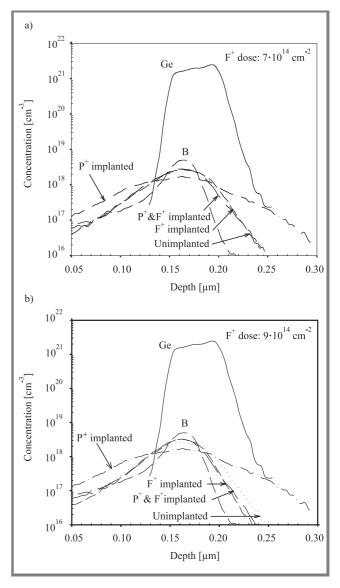

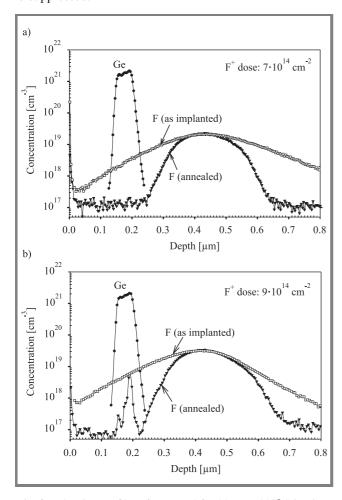

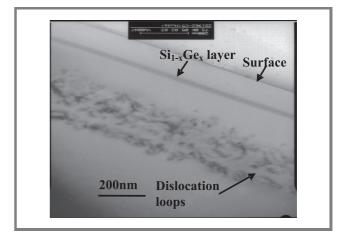

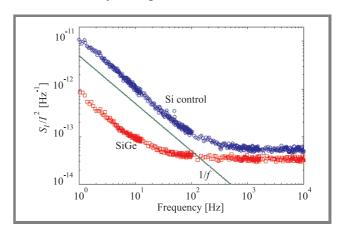

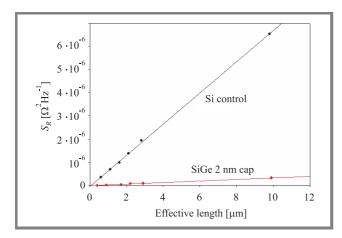

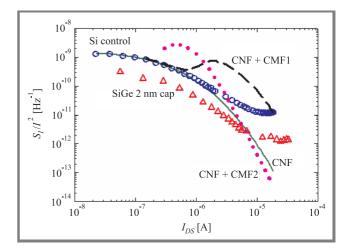

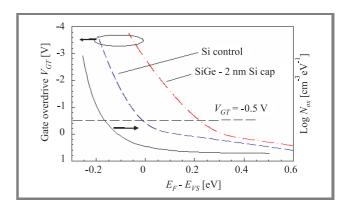

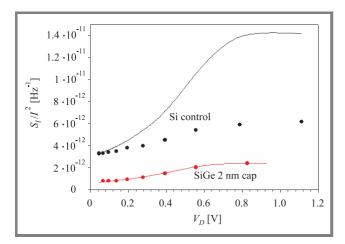

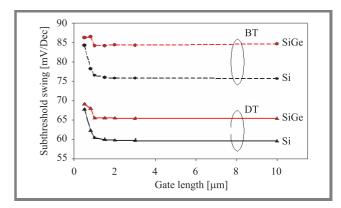

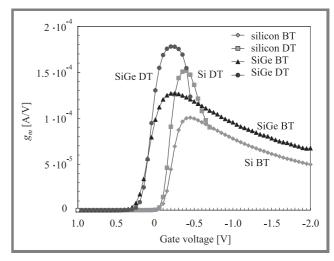

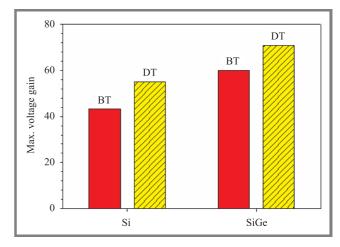

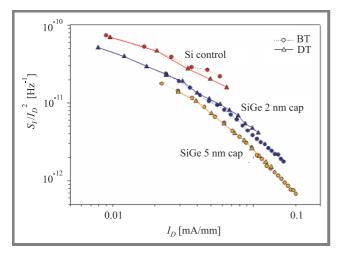

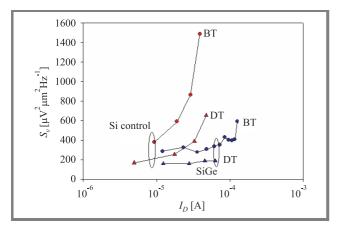

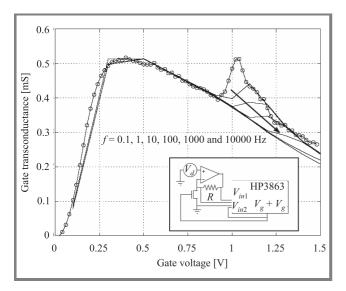

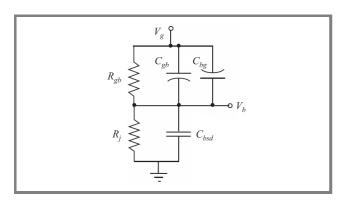

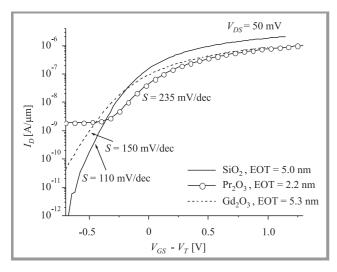

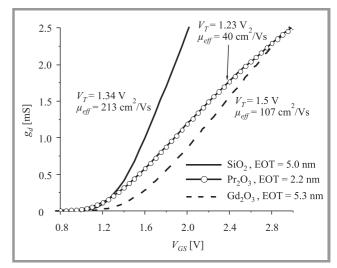

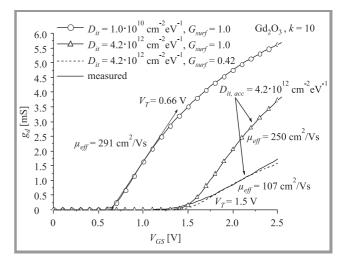

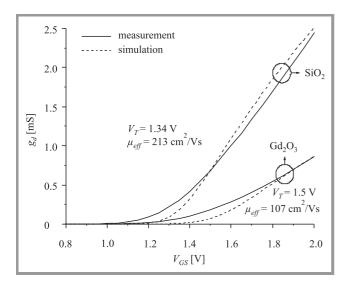

Fig. 1. High resolution SEM image of a 40 nm polysilicon nanowire, showing the effect of line edge roughness of about 4–7 nm.